关于仿真里的后门访问,之前的文章《三分钟教会你SpinalHDL仿真中的后门读写》中有做过介绍,其针对的都是针对以SpinalHDL中的代码进行的后门访问。今天来看看当封装了Verilog BlackBox时,在Sp

2023-07-15 10:22

UVM里面有前门访问,后门访问的概念。前门访问无非通过总线来实现寄存器/Mem的访问。而当在一些仿真中为了减少通过总线进行配置下发所需的时间,那么后门访问就非常便捷了,它使得无需通过总线即可修改寄存器/Mem的值。今天,就来看看在SpinalHDL的仿真中我们可以

2022-09-02 09:29

使用后门方式测量时钟频率的需求来源更多是SOC验证的场景,由于SOC的规模较大,一次编译时间成本较高,在N个小时级别。如果采用前门方式,比如编写测量频率的module或者interface,一旦有新的测量需求则就需要TB重新连接时钟信号,重新编译环境。

2023-09-24 11:34

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

2025-05-14 09:36

当编译选项没有使用-debug_all,使用的是-debug_access+all或者-debug_access+r+w+f。而恰好信号所在的模块为cell时,也无法正常进行后门访问。

2023-06-16 12:53

可以使用任意方式来跑跨域MPLS(A、B、C1、C2都可以),不过关于传递Vpnv4路由的配置此处不做介绍;此处只介绍关于PE和CE对接的配置和关于后门链路的配置

2023-10-16 16:54

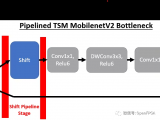

在这个项目中,将在线和离线 TSM 网络部署到 FPGA,通过 2D CNN 执行视频理解任务。 介绍 在这个项目中,展示了 Temporal-Shift-Module ( https

2023-07-07 10:47

FPGA语言,即现场可编程门阵列编程语言,是用于描述FPGA(Field Programmable Gate Array)内部硬件结构和行为的特定语言。它允许设计师以硬件描述的方式定义FPGA的逻辑

2024-03-15 14:50

本文首先介绍了高级语言的优缺点、汇编语言的优缺点及使用汇编语言的理由,其次介绍了机器语言的优缺点,最后阐述了高级语言和汇

2018-04-16 10:28

VB语言和C++语言是两种不同的编程语言,虽然它们都属于高级编程语言,但在设计和用途上有很多区别。下面将详细比较VB语言

2024-02-01 10:20