时钟芯片最基本的作用就是显示时间和记录时间的时钟作用,而且时钟芯片的的时钟

2018-01-30 15:24

说明 可以使用该指令读取 CPU 时钟的当前日期和当前时间(模块时间)。 在此指令的 OUT 输出参数中输出读取的日期。得出的值不包含有关本地时区或夏令时的信息。 说明 CPU

2023-06-28 16:18

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34

时钟芯片是RTC集成电路,也被称为实时时钟。任何实时时钟的核心都是晶振,晶振频率为32768 Hz ,它为分频计数器提供精确的与低功耗的实基信号,可以用于产生秒、分、时、日等信息,也就是说

2020-11-16 17:15

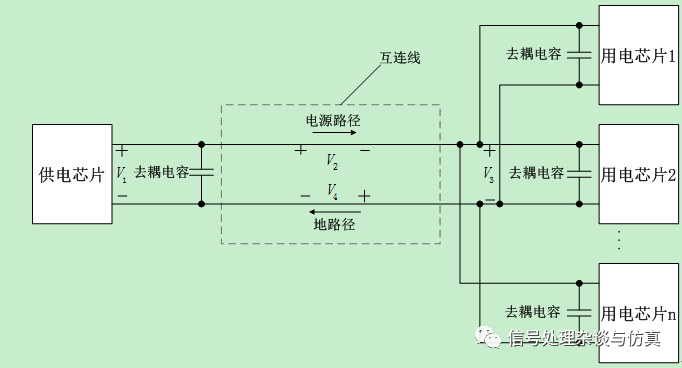

时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错。

2020-06-26 10:37

一类问题是与信号路径相关的反射问题和相邻路径间的串扰问题,这类问题都与信号的上升时间和时钟工作频率有关,称之为信号路径问题。

2023-10-31 10:37

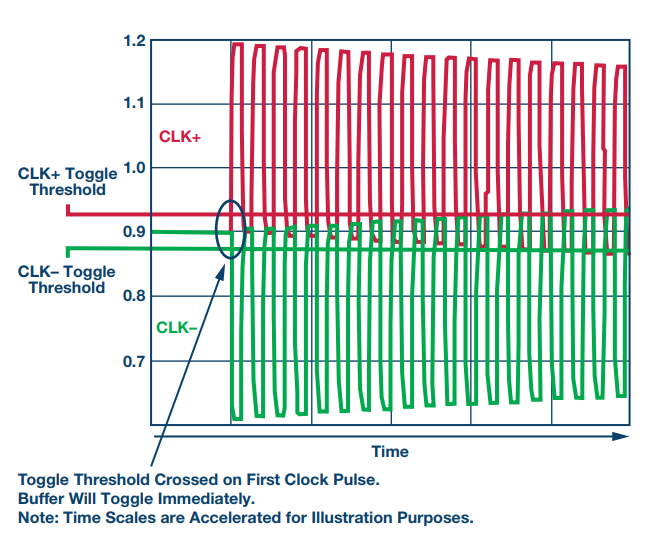

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长。 令人惊讶的是,这种延迟的原因往往是错误的启动

2023-01-05 11:07

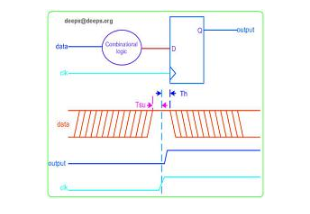

触发器是FPGA设计中最常用的基本器件。触发器工作过程中存在数据的建立(setup)和保持(hold)时间。对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定

2018-08-18 09:50

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成

2018-03-11 10:07