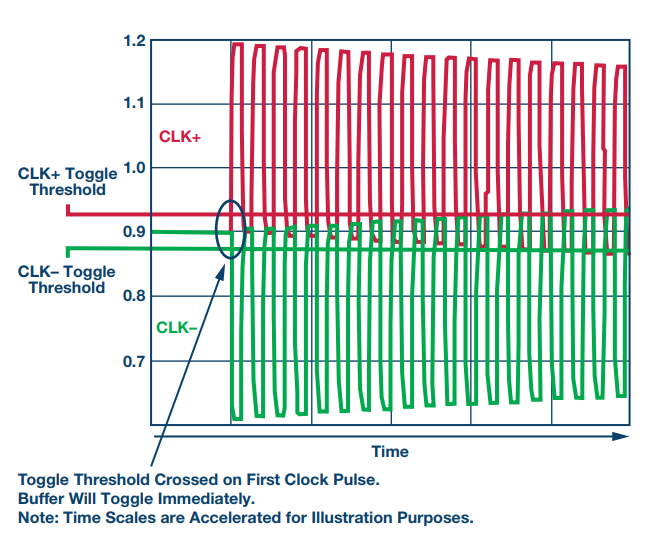

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样

2023-01-05 11:07

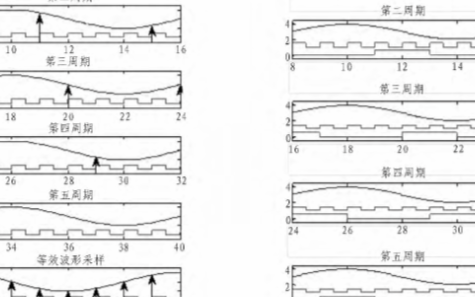

的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。

2018-11-08 09:56

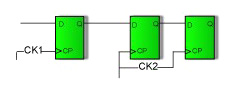

的情况下,时间交叉采样法是最佳的选择。伴随着低价、高速、可配置的数字硬件平台(DSP、FPGA、CPLD和ASIC等)的出现,新的数字处理技术的发展已经为时间

2020-07-21 10:52

说明 可以使用该指令读取 CPU 时钟的当前日期和当前时间(模块时间)。 在此指令的 OUT 输出参数中输出读取的日期。得出的值不包含有关本地时区或夏令时的信息。 说明 CPU

2023-06-28 16:18

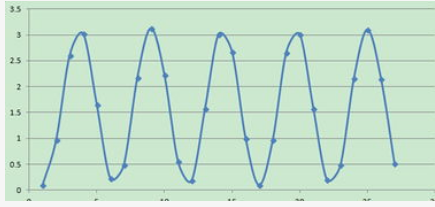

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为71.5,则ADC

2019-10-14 16:22

的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。

2020-03-12 10:22

接收机ADC对接收到的连续波形进行采样,发射机的DAC与接收机的ADC不可能具有完全相同的时钟频率和相位。时域的采样偏差导致频域上子载波不再正交,对于OFDM来说这是致命的。

2017-02-11 14:16

时钟芯片是RTC集成电路,也被称为实时时钟。任何实时时钟的核心都是晶振,晶振频率为32768 Hz ,它为分频计数器提供精确的与低功耗的实基信号,可以用于产生秒、分、时、日等信息,也就是说

2020-11-16 17:15

片上系统(SOC)设计的最大挑战之一是不同的块在独立时钟上运行。通过处理器总线,存储器端口,外围总线和其他接口集成这些块可能很麻烦,因为当异步接口未正确同步时可能导致不可预测的行为。

2019-09-14 16:50