引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。

2022-07-22 09:46

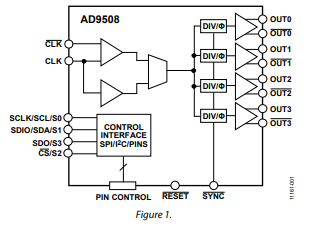

AD9508提供时钟扇出能力,针对能使系统性能达到优质的低抖动进行设计。这款器件能满足时钟数据转换器等应用所需的相位噪声和低抖动要求,可优化这些应用的性能。

2025-04-10 14:05

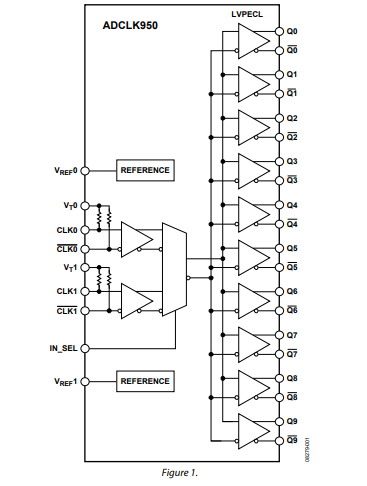

ADCLK950是一款超快时钟扇出缓冲器,采用ADI公司专有的XFCB3硅-锗(SiGe)双极性工艺制造,设计用于要求低抖动的高速应用。

2025-04-11 09:43

该属性会将每个驱动程序的扇出限制告知工具,并通过指示布局器了解扇出限制来指引该工具对高扇出的负载进行分配。此属性可同时应用于 FF 与 LUT 驱动程序。当 MAX_FANOUT 值小于约束的信号线的实际

2025-08-28 10:47

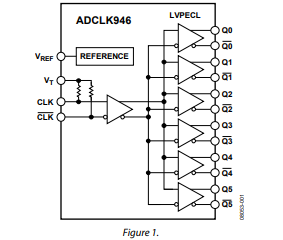

ADCLK946是一款采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造的超快型时钟扇出缓冲器。这款器件设计用于要求低抖动性能的高速应用。 这款器件具有一个带中心抽头、差分、100

2025-04-11 10:31

高扇出信号线 (HFN) 是具有大量负载的信号线。作为用户,您可能遇到过高扇出信号线相关问题,因为将所有负载都连接到 HFN 的驱动程序需要使用大量布线资源,并有可能导致布线拥塞。鉴于负载分散,导致进一步增大信号线延迟,因此在高

2025-08-28 10:45

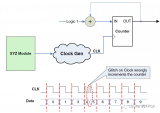

组合逻辑生成的时钟,在FPGA设计中应该避免,尤其是该时钟扇出很大或者时钟频率较高,即便是该时钟通过BUFG进入全局

2020-10-10 10:28

扇出型封装一般是指,晶圆级/面板级封装情境下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。扇出型封装的核心要素就是芯片上的RDL重布线层(可参考下面图表说明

2023-11-27 16:02

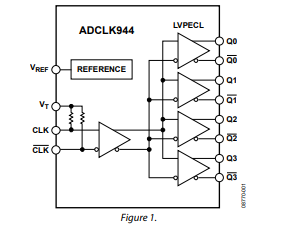

KADCL944是一款超快型时钟扇出缓冲器,采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造。这款器件设计用于要求低抖动性能的高速应用。 该器件具有一路配中心抽头、差分、100

2025-04-10 16:23

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17