本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信号与高频信号的区别,分析了25MHz时钟信号沿上的回沟等细节的测试准确度问题,并给出了高速信号测试时合理选择示波器的一些建议。

2023-06-13 11:02

本文主要为25mHZ石英晶体振荡器电路图,并对其进行了分析说明:

2016-05-24 11:46

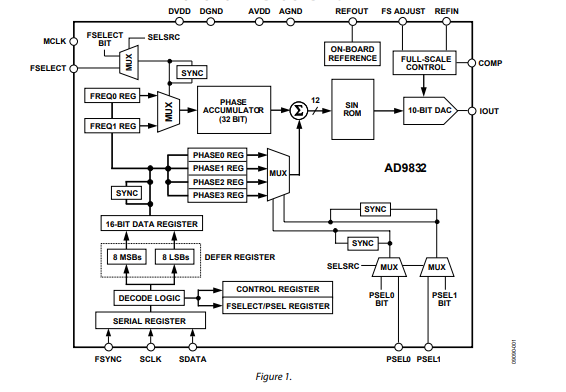

AD9832是一款数控振荡器,在单个CMOS芯片内集成了一个相位累加器、一个正弦查找表以及一个10位数模转换器(DAC),提供相位调制和频率调制两种调制能力。 最高支持25 MHz

2025-05-06 15:15

交换芯片+主控CPU,CPU通过SMI控制交换芯片,CPU提供复位信号和25MHz时钟给交换芯片,交换芯片与CPU数据报文交互通过RMII。主控CPU在boot汇编代码执行交换芯片的复位和25MHz

2019-01-12 09:09

晶振频率是晶体振荡器的固有频率,而时钟频率是以时间为准的振荡频率,一个时钟

2022-01-29 16:57

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,

2023-09-20 14:17

)在单位时间内所出现的脉冲数量多少的计量名称;频率的标准计量单位是Hz(赫)。本文主要介绍什么是时钟频率及编程,具体的跟随小编一起来了解一下。

2018-04-28 09:49

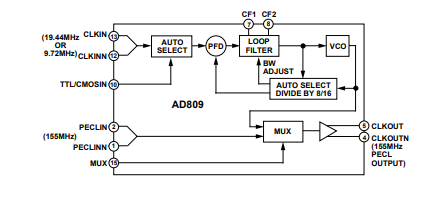

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟

2017-11-18 12:08

AD809可以从19.44 MHz或9.72 MHz TTL/CMOS/ECL/PECL基准频率产生155.52 MHz ECL/PECL输出

2025-04-27 15:12

输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100

2018-04-24 11:20