时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。

2018-03-11 10:07

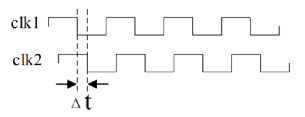

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导

2022-10-26 09:04

首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边

2018-12-06 11:53

当触发器输入端的数据和触发器的时钟不相关时,很容易导致电路时序约束不满足。本章主要解决模块间可导致时序 violation 的异步问题。

2023-03-28 13:46

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此

2017-11-16 01:01

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主

2017-02-11 11:34

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,通过时钟

2023-09-20 14:17