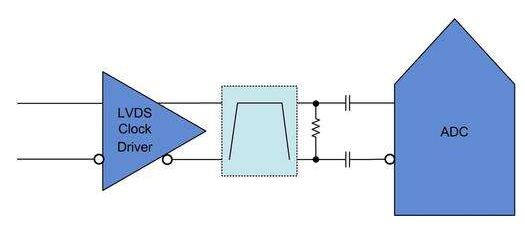

当ADC时钟输入时,都需要考虑哪些因素呢?如何做才能使ADC充分发挥芯片的性能呢?让ADI公司数字视频处理部高级工程师Ian Beavers告诉你吧! 为了充分发挥芯片的性能,应利用一个差分信号驱动

2017-12-19 04:10

通过时钟电路进入ADC的任何噪声都可能直接进入输出。ADC中涉及该电路的噪声机制可以被认为是混频器。在查看噪声时以这种方式考虑此输入确实可以正确看待事物。通过时钟输入进

2023-06-30 17:00

触发器是数字电路中的一种基本逻辑单元,用于存储和操作信息。它能够在特定的输入条件下改变输出状态,并在没有进一步输入时保持输出状态不变。时钟输入是触发器的一个重要组成部分

2024-08-12 10:49

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

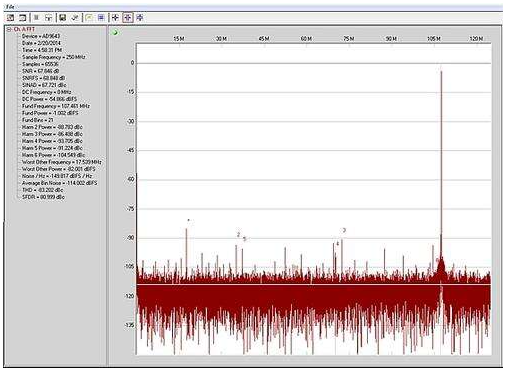

使用了AD9643评估板,该评估板可以配置为使用AD9523驱动AD9643的时钟输入。如图2所示,我们有AD9643评估板、HSC-ADC-EVALZ数据采集板、墙上电源、罗德施瓦茨SMA100信号发生器和PC。

2023-06-30 16:42

在本例中,我们将研究如何利用低抖动时钟发生器AD9643对双通道14位250 MSPS ADC进行计时。使用这些特定产品的常见时钟频率为9523.245 MHz,因此我们将为AD76使用30.72 MHz基准电压源(外部振荡器),并设置内部寄存器,为AD9523生

2023-06-30 16:59

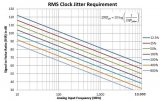

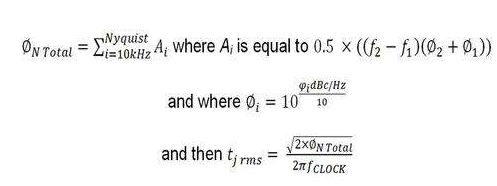

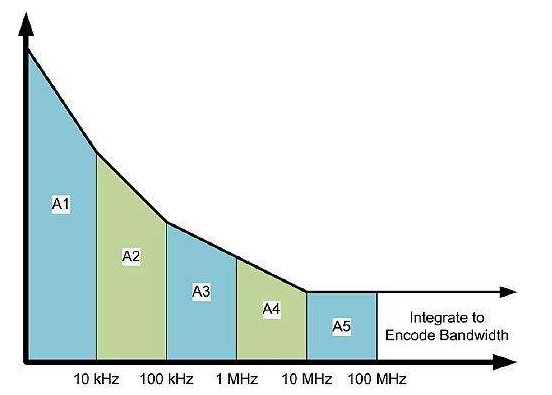

这是为数不多的跨越围栏是有利的情况之一。目前市面上的许多时钟产品都指定器件的相位噪声,而不指定抖动。让我们来看看如何从相位噪声变为抖动。然后,我们将能够预测具有一定抖动的ADC的SNR。一个例子将不得不等待,因为我在这里只有这么多空间。现在让我们专注于数学。下图显示了我们如何根据

2023-06-30 16:58

ADuM4165/ADuM4166^1^ 是 USB 2.0 端口隔离器,利用 ADI 公司的 *i*Couple^® ^技术,可根据需要,来动态支持所有 USB 2.0 数据速率,包括低速 (1.5 Mbps)、全速 (12 Mbps) 或高速 (480 Mbps)。这些套件支持具有自动速度协商的主机隔离以及外设隔离。

2025-05-29 15:46

TB67S109A是一款两相双极步进电机驱动器,采用PWM斩波器。解码器的时钟是内置的。采用BiCD工艺制造,额定值为50V/4.0A。

2025-05-13 09:55

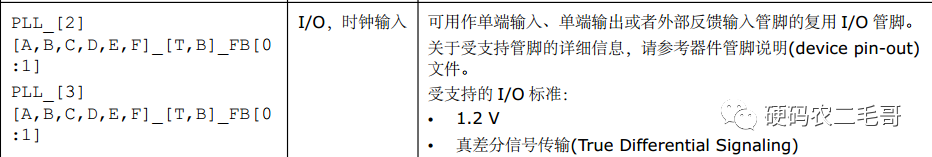

几年前FPGA时钟只需要连接一个单端输入的晶振,非常容易。现在不同了,差分时钟输入,差分信号又分为LVDS和LVPECL,时钟

2023-08-21 11:28