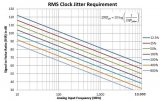

当ADC时钟输入时,都需要考虑哪些因素呢?如何做才能使ADC充分发挥芯片的性能呢?让ADI公司数字视频处理部高级工程师Ian Beavers告诉你吧! 为了充分发挥芯片的性能,应利用一个差分信号驱动

2017-12-19 04:10

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

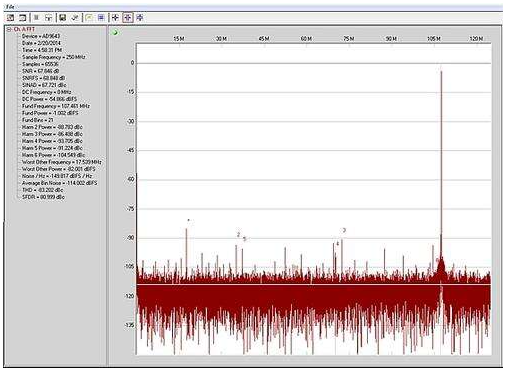

使用了AD9643评估板,该评估板可以配置为使用AD9523驱动AD9643的时钟输入。如图2所示,我们有AD9643评估板、HSC-ADC-EVALZ数据采集板、墙上电源、罗德施瓦茨SMA100信号发生器和PC。

2023-06-30 16:42

ADuM4165/ADuM4166^1^ 是 USB 2.0 端口隔离器,利用 ADI 公司的 *i*Couple^® ^技术,可根据需要,来动态支持所有 USB 2.0 数据速率,包括低速 (1.5 Mbps)、全速 (12 Mbps) 或高速 (480 Mbps)。这些套件支持具有自动速度协商的主机隔离以及外设隔离。

2025-05-29 15:46

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。

2022-07-14 09:15

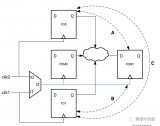

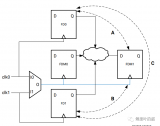

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时clk0和clk1还分别驱动了其他逻辑。

2023-12-19 12:56

本文主要介绍了CD40110组成的一位数码计数器。CD40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。CD40110有2个计数时钟输入端

2018-03-04 11:17

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时clk0和clk1还分别驱动了其他逻辑。

2023-12-11 13:55

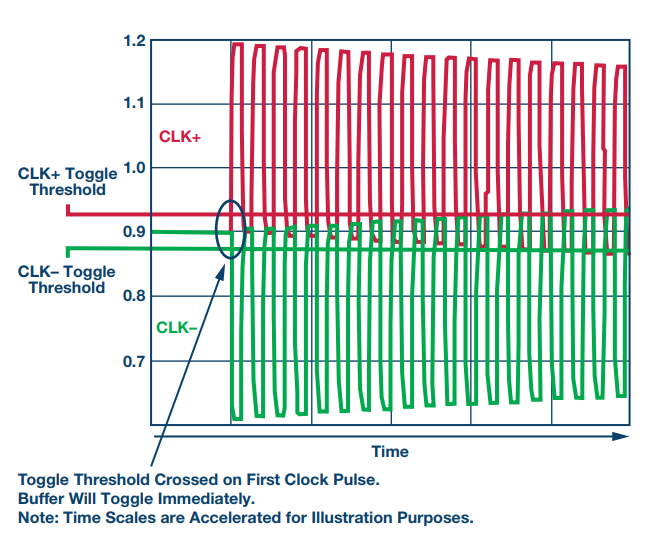

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长。 令人惊讶的是,这种延迟的原因往往是错误的启动

2023-01-05 11:07

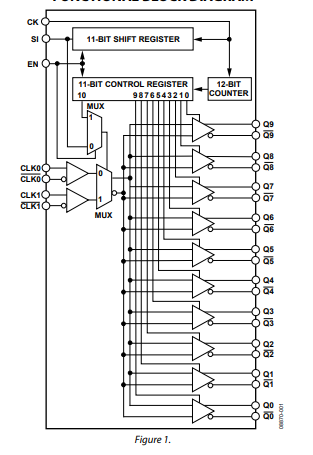

ADN4670是一款低压差分信号(LVDS)时钟驱动器,可以将一路差分时钟输入信号扩展为十路差分时钟输出。这款器件可以通过简单的串行接口进行编程,以便选择两路

2025-04-10 16:19