在这篇文章中,我将会介绍一个有趣的时钟芯片反馈装置。它可能意外发生,或作为尝试恢复或测试模式,但通常应该如所

2017-11-01 06:56

1 RTC结构特点实时时钟的基本功能是保持跟踪时间和日

2006-04-17 20:04

遵循良好的设计准则,选择合适的时钟树拓扑结构,采用高质量的芯片是非常好的做法,但这也并不能保证时钟是完全令人满意的。很多其他的因素也可以引入抖动,例如不匹配的信号线长度,EMI,电压波动甚至机械应力(影响晶体的压电特性),这些因素都是不可预测的。

2019-08-20 10:44

在当前的数字集成电路设计中,同步电路占了绝大部分。所谓同步电路,即电路中的所有寄存器由为数不多的几个全局时钟驱动,被相

2018-07-12 09:02

引言 随着电子技术的不断发展,数据的传输速度越来越快,高速时钟的应用日益广泛,如何保证时钟在高速跳变过程中的信号完整性、抖动、功耗等问题,已

2010-11-03 11:05

在高速数字系统中,时钟信号通常采用传输线进行传输,因此了解信号在传输线的传播速度十分必要。

2020-12-08 10:54

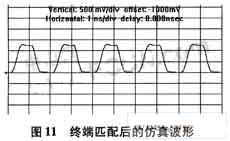

目标芯片的一个常见问题是信号的终止。如果没有适当的终止,将会发生阻抗不匹配,并且能量将反射到线路上。这些脉冲可能非常大,以至于使器件错误的触发,导致电路错误操作(并且可能是灾难性的)。

2018-10-11 08:17

ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。在A/D转换过程中引入的噪声来

2010-10-26 11:20

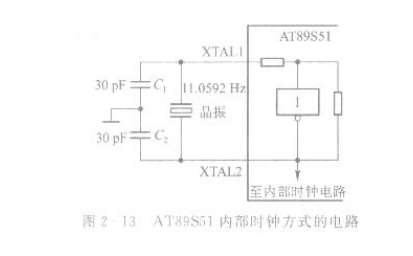

AT89S51内部有一个用于构成振荡器的高增益反相放大器,它的输入端为芯片引脚XTAL1,输出端为引脚XTAL2。这两个引脚跨接石英晶体和微调电容,构成一个稳定的自激振荡器,图2-13是AT89S51内部时钟方式的电路

2019-05-07 15:50

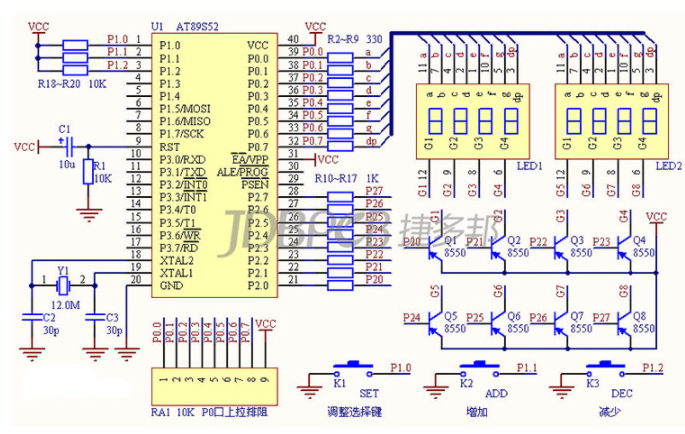

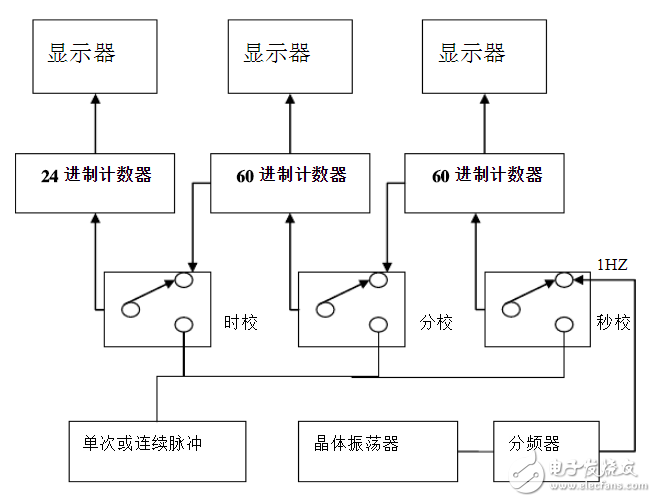

多功能数字钟是一个对标准频率(1HZ)进行计数的计数电路。它由振荡器、分配器、计数器、译码器和显示电路组成。振荡器与分配器组成秒脉冲输出装置,秒脉冲信号输入计数器进行计数,并把累计结果以“时”、“分

2018-01-26 09:52