在当前的数字集成电路设计中,同步电路占了绝大部分。所谓同步电路,即电路中的所有寄存器由为数不多的几个全局时钟驱动,被相

2018-07-12 09:02

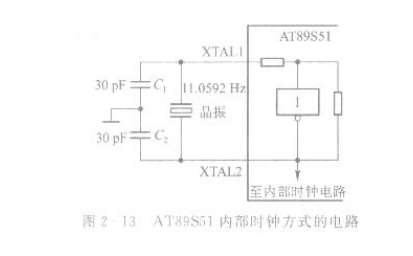

AT89S51内部有一个用于构成振荡器的高增益反相放大器,它的输入端为芯片引脚XTAL1,输出端为引脚XTAL2。这两个引脚跨接石英晶体和微调电容,构成一个稳定的自激振荡器,图2-13是AT89S51内部时钟方式的电路

2019-05-07 15:50

本文分别介绍了不同四款单片机时钟设计电路图,另外还将它们的程序详细的表达了出来。

2018-01-26 16:19

晶体与晶振在电路设计中的应用十分广泛,对于数字电路,一个稳定的时钟信号,是系统稳定的前提。

2023-11-22 10:44

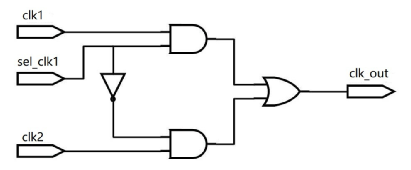

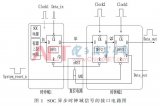

随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两个时钟源有可能是同源且频率比呈倍数关系,也有可能是不相关的。直接使用选择逻辑进行

2023-03-29 11:41

针对当前SOC内部时钟越来越复杂、接口越来越多以及亚稳态、漏信号等常见的各种问题,分析了以往的优化方法的优缺点,然后从电路的角度出发,提出了一种新的SOC跨时钟域同步电路设计

2018-02-09 14:30

通常情况下,时钟的分频在FPGA设计中占有重要的地位,在此就简单列出分频电路设计的思考思路。

2020-07-10 17:18

工欲善其事必先利其器,工程师要想设计出优秀的电路,首先就要有功能强劲的电路设计软件。本文总结了数款主流的电子电路设计软件,为工程师的电路设计提供参考。##Protues

2014-09-03 10:22

通常我们在设计芯片的同时,可以根据芯片本身的特征,额外地把可测性电路设计(Design For Testability)在芯片里。谈到可测性的电路设计,内建自测试(BIST)和基于扫描Scan—Based)的电路设计

2011-06-10 10:13

电路设计流程包括电路需求分析、电路设计、电路仿真和电路测试等环节。初学者需要了解这些环节的作用,并能够按照流程进行

2023-05-09 14:32