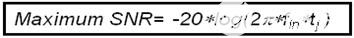

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19

对于频率成分相对较低的输入信号,例如在1MHz以下,时钟抖动变得不那么重要,但是当输入信号的频率为几百兆赫兹时,时钟上的抖动将成为误差的主要来源,并且将成为SNR的限制

2023-01-03 14:35

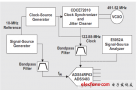

通过上一期我们了解到:数字电子产品中电源轨噪声和时钟抖动是有关联的,以及测量电源轨噪声的方案,接下来我们基于实际测量,揭示电源轨噪声对系统时钟抖动的影响。

2024-11-22 16:11

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能

2019-09-14 11:24

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(

2023-04-04 09:20

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的

2012-05-07 11:37

本文即第2部分中,这种组合抖动将用于计算ADC的信噪比 (SNR),之后将其与实际测量情况进行比较。

2012-05-07 11:31

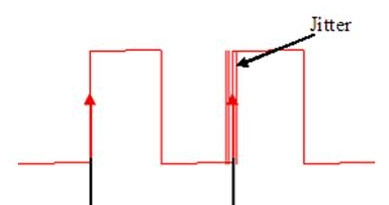

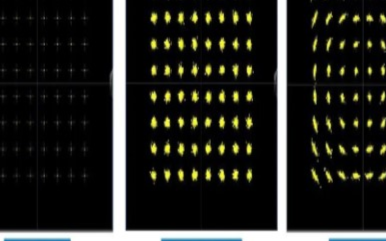

在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但不幸的是,这种信号并不存在。如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。

2018-03-13 10:21

抖动一般定义为信号在某特定时刻相对于其理想位置的短期偏移。这个短期偏移在时域的表现形式为抖动(下文的抖动专指时域抖动),在频域的表现形式为相噪。本文主要探讨下

2016-01-18 10:54

相噪是衡量频谱纯度的一个重要指标,表征的是频率的短期稳定度。单边带相位噪声L(f)来源于相位的波动,单位为 dBc/Hz,传统上定义为特定频偏处1 Hz带宽内的单边带(SSB)功率与载波功率之比,后在IEEE新版本中L(f) 定义更新为随机相位波动φ(t) 单边带功率谱密度Sφ(f) 的一半。

2022-01-19 15:26