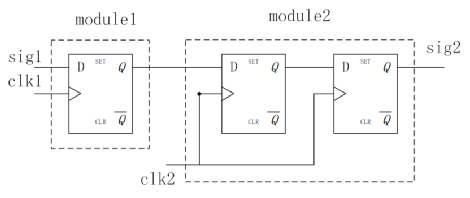

时钟域clock domain:以寄存器捕获的时钟来划分时钟域。 单时钟

2022-08-29 15:11

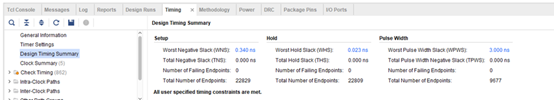

本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟

2022-08-02 11:44

时钟域clock domain:以寄存器捕获的时钟来划分时钟域。单时钟

2022-12-26 15:21

在很久之前便陆续谈过亚稳态,FIFO,复位的设计。本次亦安做一个简单的总结,从宏观上给大家展示跨时钟域的解决方案。

2024-01-08 09:42

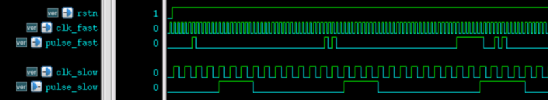

慢时钟域采集从快时钟域传输来的信号时,需要根据信号的特点来进行同步处理。对于单 bit 信号,一般可根据电平信号和脉冲信号来区分。

2023-03-28 13:52

单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single,如下图代码所示。参数DEST_SYNC_FF决定了级联触发器

2023-08-16 09:53

FIFO是实现多位宽数据的异步跨时钟域操作的常用方法,相比于握手方式,FIFO一方面允许发送端在每个时钟周期都发送数据,另一方面还可以对数据进行缓存。需要注意的是对FIFO控制信号的管理,以避免发生

2023-05-11 14:01

想象一下,如果频率较高的时钟域A中的信号D1 要传到频率较低的时钟域B,但是D1只有一个时钟脉冲宽度(1T),clkb

2019-02-04 15:52

理论上讲,快时钟域的信号总会采集到慢时钟域传输来的信号,如果存在异步可能会导致出现时序问题,所以需要进行同步处理。此类同步处理相对简单,一般采用为延迟打拍法,或延迟采样

2023-03-28 13:50

跨时钟域的问题:前一篇已经提到要通过比较读写指针来判断产生读空和写满信号,但是读指针是属于读时钟域的,写指针是属于写时钟

2018-09-05 14:29