时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34

这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43

所有的数字电路都需要依靠时钟信号来使组件的运作同步,每单位时间内电路可运作的次数取决于时钟的频率,因此时钟运作的频率即被大家视为系统运作的性能指针。

2018-07-21 10:40

最近有客户购买一块开发板ZC706,打算调试GT光口部分。发现开发板没有给GT的参考时钟,原理图如下:

2017-02-23 12:11

在PCB板子过回焊炉容易发生板弯及板翘,大家都知道,那么如何防止PCB板子过回焊炉发生板弯及

2019-05-03 14:06

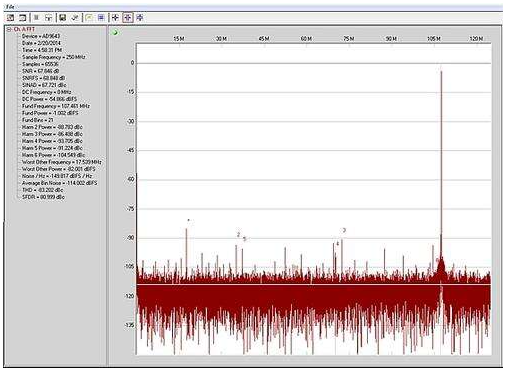

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能

2023-04-11 11:06

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。

2019-08-07 17:51

本项目是基于启明RA6M5开发板搭载2.4寸液晶屏的电子时钟,该电子时钟有两个模式——正常模式和低功耗模式,可以通过开发板的按键改变

2023-12-25 12:26

使用了AD9643评估板,该评估板可以配置为使用AD9523驱动AD9643的时钟输入。如图2所示,我们有AD9643评估板、HSC-ADC-EVALZ数据采集

2023-06-30 16:42