时钟分频及定时变换电路

2009-10-11 10:35

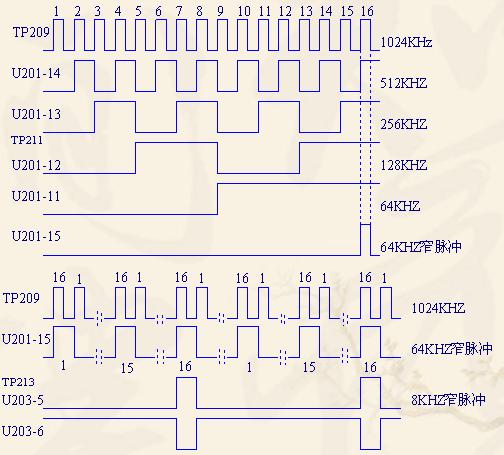

摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使

2017-11-30 09:14

单片机都是有时钟振荡器的。还有定时器,看门狗,程序计数器等等。如果看门狗或者定时器所要求的脉冲速度比较时钟脉冲慢,那么,就要利用分频器进行分频,以得到你所要求的脉冲速率

2017-11-15 10:07

如果cpu是计算机的大脑,电流是计算机的血液,那么时钟则是计算机的心脏,时钟频率决定了处理器运算的快慢,它的每一次“跳动”都驱动着处理器不停的执行命令。不同的是,人的各个部位心率是一样的,但计算机

2017-11-15 09:33

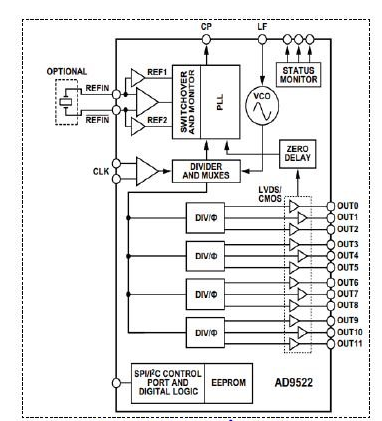

在集成度高度发展的今天,不能靠多个晶振源来解决问题,而且一旦晶振固定那么它的灵活性和可移植性必然受到很大影响,所以一些时钟分频芯片应运而生,今天我们将举一个很有代表性的AD9522时钟

2018-03-16 16:31

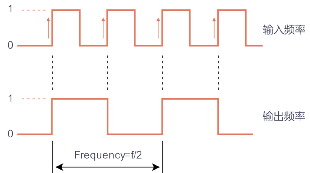

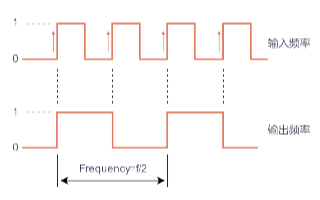

采用触发器反向输出端连接到输入端的方式,可构成简单的 2 分频电路。

2023-05-30 17:21

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频

2023-01-05 14:00

和单片机一样,FPGA开发板上也都会配有晶振用来生成板载时钟。前一篇我们提到了小脚丫的固定板载时钟频率为12MHz,这个频率实际上就是作为我们的时间参考基准。

2023-06-20 17:02

和单片机一样,FPGA开发板上也都会配有晶振用来生成板载时钟。前一篇我们提到了小脚丫的固定板载时钟频率为12MHz,这个频率实际上就是作为我们的时间参考基准。正如歌里唱的那样: 嘀嗒嘀嗒嘀嗒嘀嗒

2021-01-06 17:02