reg2reg路径约束的对象是源寄存器(时序路径的起点)和目的寄存器(时序路径的终点)都在FPGA内部的

2023-06-26 14:28

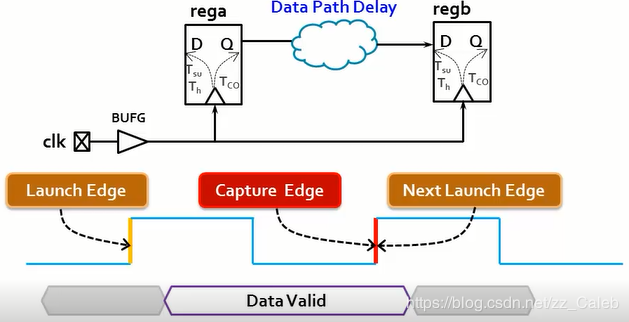

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54

时序路径 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标

2020-11-17 16:41

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序

2022-05-04 17:13

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50

边沿。 ④ 通常情况下这两个边沿会有一个时钟周期的差别。 2、时序路径 (Timing path典型时序路径有四种) ① ② 第一类

2020-11-25 15:27

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37

更为具体的时序报告信息如何从中获取,或者如何根据时序报告发现导致时序违例的潜在原因呢?

2020-09-04 10:24

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型的特征:数据多个周期翻转一次,如下图所示。因此,我们把这种路径称为多周期路径

2023-09-14 09:05