典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型的特征:数据多个周期翻转一次,如下图所示。因此,我们把这种路径称为多周期路径

2023-09-14 09:05

(1)从输入端口到内部寄存器(从D_IN经过组合逻辑1,到第一个寄存器数据端口D)。 (2)从内部寄存器到内部寄存器(从第一个寄存器的Q端,经过组合逻辑2,到第二个寄存器的D端)。 (3)从内部寄存器到输出端口( 从第二个寄存器的Q端,经过组合逻辑3,到输出端口 D_O端)。 (4)从输入端口到输出端口(从D_IN经过组合逻辑4到达输出端口D_O)。

2018-10-06 09:00

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set

2025-04-23 09:50

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序

2022-08-02 09:25

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序

2023-06-28 09:38

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“

2023-08-08 10:31

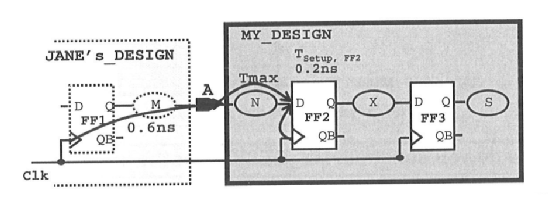

设置 Input-to-Reg 时序路径的约束时,不仅需要创建时钟模型,还需要设置输入延时 (input delay)。设置 input delay 时,需要假设输入 port 信号是与时钟

2023-03-31 16:39

我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC

2017-11-18 04:04

PrimeTime 进行静态时序分析时把整个芯片按照时钟分成许多时序路径。路径的起点是时序单元的输出引脚或是设计的输入端

2018-06-22 14:40