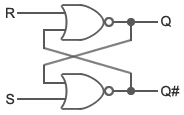

在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「

2016-08-01 10:58

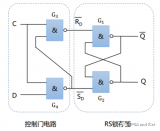

从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

2022-10-10 15:39

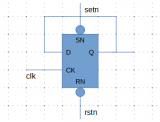

“时钟是时序电路的控制者” 这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。但是

2018-07-21 10:55

「组合电路」是根据当前输入信号的组合来决定输出电平的电路。换言之,就是现在的输出不会被过去的输入所左右,也可以说成是,过去的输入状态对现在的输出状态没有影响的电路。

2021-01-09 11:12

时序逻辑电路对于组合逻辑的毛刺具有容忍度,从而改善电路的时序特性。同时电路的更新由时钟控制。

2018-11-24 11:17

时序电路是数字电路的基本电路,也是FPGA设计中不可缺少的设计模块之一。

2020-09-08 14:21

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,避免使用Latch(锁存器)一直是个绕不开的话题,本文结合网上的文章,并根据示例介绍如何在实际设计中避免Latch。

2023-08-08 09:55

有朋友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

2024-02-20 16:12

(1)从输入端口到内部寄存器(从D_IN经过组合逻辑1,到第一个寄存器数据端口D)。 (2)从内部寄存器到内部寄存器(从第一个寄存器的Q端,经过组合逻辑2,到第二个寄存器的D端)。 (3)从内部寄存器到输出端口( 从第二个寄存器的Q端,经过组合逻辑3,到输出端口 D_O端)。 (4)从输入端口到输出端口(从D_IN经过组合逻辑4到达输出端口D_O)。

2018-10-06 09:00

既然时序电路是有记忆功能地,那有几个概念必须是要清楚的:输入信号、输出信号、激励信号以及现态、次态及其转换关系。

2020-08-08 10:19