本文开始介绍了什么是锁存器与锁存器的工作原理,其次介绍了锁存器的作用与锁存器的应用实例,最后介绍了常用74系列锁存器芯片

2018-01-31 16:30

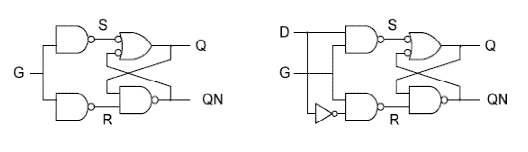

用或非门组成的基本SR锁存器。

2023-02-27 10:29

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题

2018-01-31 13:57

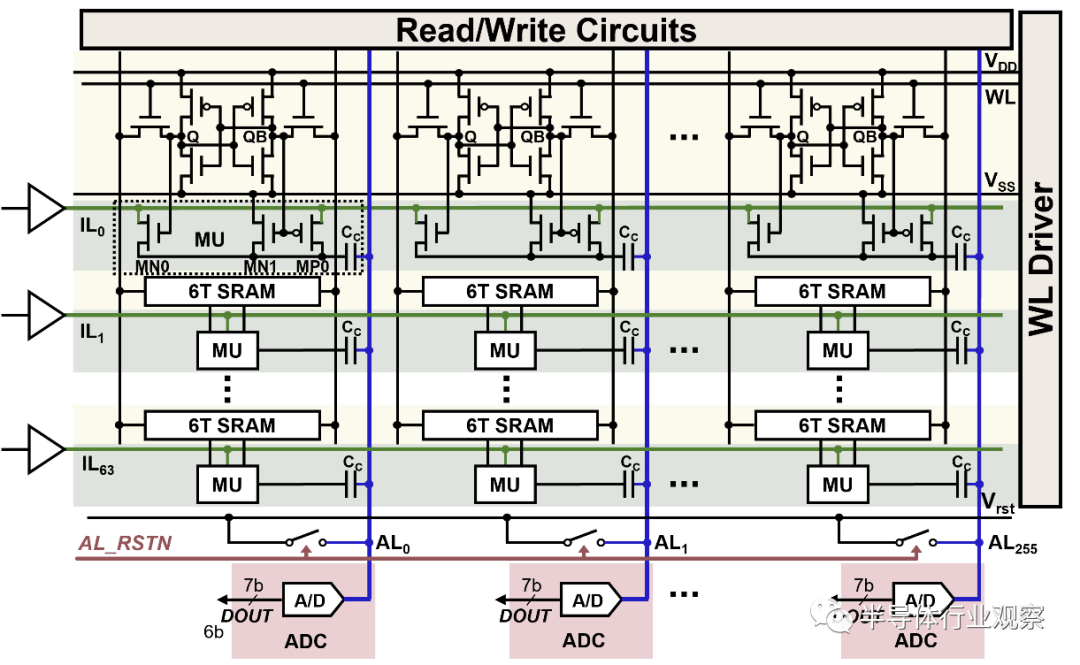

作为后摩尔时代发展的必然趋势之一,存算一体越来越受到行业的关注。在存算十问的前六问中,我们梳理了存算一体的技术路线、挑战和通用性等问题,这一次我们从技术的壁垒入手,邀请

2023-09-22 14:16

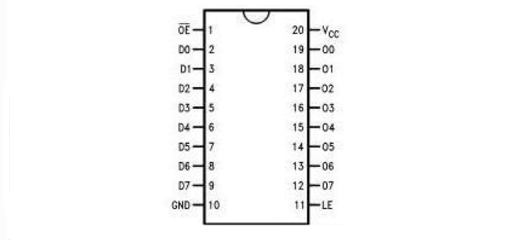

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48

基本约束条件: SR锁存器是一种基本的数字逻辑电路,用于存储一位二进制信息。它有两个输入端:S(Set)和R(Reset),以及两个输出端:Q和Q'(Q的反相)。以下是SR锁存器的基本约束条件

2024-07-23 11:34

人工智能时代对计算芯片的算力和能效都提出了极高要求。存算一体芯片技术被认为是有望解决处理器芯片“存储墙”瓶颈,大幅提升人工智能算力能效和算力密度的关键技术和重要解决方案。SRAM存算一体芯片技术由于

2024-01-02 11:02

的“存储墙”、“功耗墙”问题。存算一体将存储与计算有机融合以其巨大的能效比提升潜力,有望成为数字经济时代的先进生产力。存算一体芯片设计迭代和投产的效率至关重要,如何能够设计出更低损耗、更低噪声、更低能耗,并符合信号完

2023-02-24 09:34