时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。

2018-03-11 10:07

注意,示波器的使用需要一定的专业知识和技能,如果不熟悉示波器的操作,建议参考示波器的使用手册或咨询专业人士。同时,切记不可在高电压电路下使用示波器,以避免对设备造成损坏或危险。

2024-05-08 17:11

最近华为发布了新版模拟器eNSP Lite的产品手册,根据产品手册描述,新版模拟器eNSP Lite基于云端发布,所以安装和登录新版模拟器eNSP Lite的方式和目前版本的eNSP有着很大

2023-05-17 10:25

首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边

2018-12-06 11:53

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导

2022-10-26 09:04

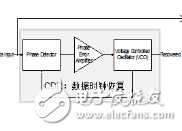

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此

2017-11-16 01:01

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26

iPhone手机的“辅助触控“大多数人都是用过,就是桌面的那个小圆点。点一下可以弹出相关的快捷启动功能。升级到IOS12版本以上,流畅度也增强了不少。

2019-05-22 10:00