SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52

下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30

学习率(learning rate)是调整深度神经网络最重要的超参数之一,本文作者Pavel Surmenok描述了一个简单而有效的办法来帮助你找寻合理的学习率。 我正

2017-12-07 11:05

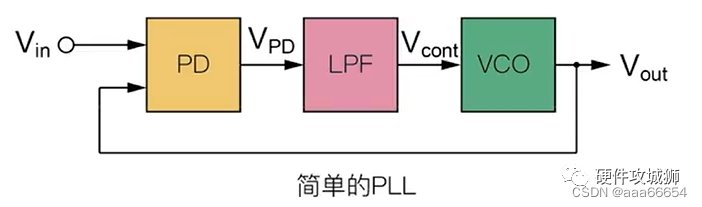

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。

2024-02-17 14:07

数字PLL(相位锁定环)在应用中遇到孤立频点失锁的情况,可能由多种因素引起。

2024-01-30 14:13

学习率是训练神经网络最重要的一个超参数,但直到最近,许多人才发现以前设置学习率的方式非常不当。去年,Leslie N. Smith在arXiv上提交了一个预印本:Cyc

2018-08-05 09:14

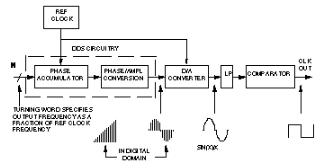

新的集成完整DDS产品为敏捷频率合成应用提供了一种有吸引力的模拟PLL替代方案。长期以来,直接数字频率合成 (DDS) 一直被认为是生成高精度、频率捷变(宽范围内可快速变化的频率)、低失真输出波形的卓越技术。

2023-01-30 09:51

受试者工作特征(ROC)曲线是另一个二分类器常用的工具。它非常类似与准确率/召回率曲线,但不是画出准确率对召回率的曲线,ROC 曲线是真正例

2018-06-19 15:20

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19