数字锁相环(DPLL),数字锁相环(DPLL)是什么? 背景知识: 随着数字电路技术的发展,

2010-03-23 15:06

数字锁相环(DigitalPhase-LockedLoop,简称DPLL)是一种基于反馈控制的技术,用于实现精确的时序控制和相位同步。通过相位比较、频率差计算、频率控制、滤波和循环控制,它能够完成

2024-01-02 17:20

实验五 数字锁相环与位同步 一、 实验目的 1. 掌握数字锁相环工作原理以及触发式数字锁

2009-04-01 09:27

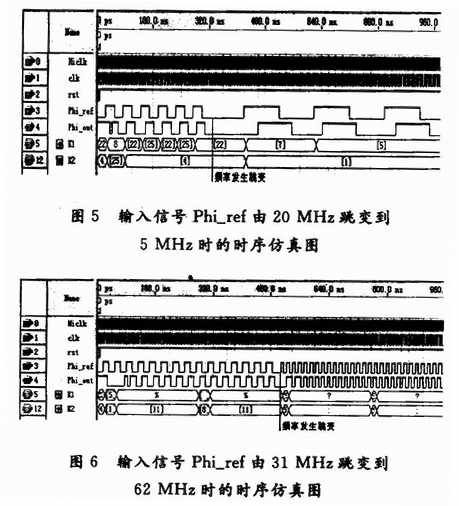

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,

2009-06-20 12:39

宽频带数字锁相环的设计及基于FPGA的实现数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应

2009-11-23 21:00

为了提高全数字锁相环的系统运行速度、降低系统功耗,同时提高锁相系统的动态性能与稳态性能,提出一种基于流

2021-04-01 11:53

本文采用一种基于比例积分(PI)控制算法的环路滤波器应用于带宽自适应的全数字锁相环,建立了该锁相环的数学模型

2010-10-14 10:03

数字锁相环(DPLL)提取位同步信号的设置涉及多个关键步骤和组件的配置。以下是一个概括性的设置流程,以及各个步骤中需要注意的关键点:

2024-10-01 15:41

锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

2023-01-31 16:31

数字锁相环(DPLL)提取位同步信号的原理主要基于相位反馈控制系统,通过不断调整接收端时钟信号的相位,使之与发送端时钟信号的相位保持一致,从而实现位同步。以下是详细的原理说明:

2024-10-01 15:38