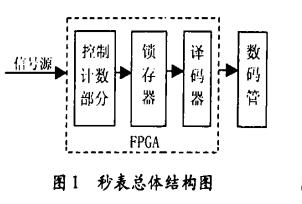

文中介绍了一种基于FPGA的数字秒表设计方法。采用VHDL硬件描述语言,运用ModelSim等EDA仿真工具。该设计具有外围电路少、集成度高、可靠性强等优点。最后经实验验证,该数字

2017-11-18 12:13

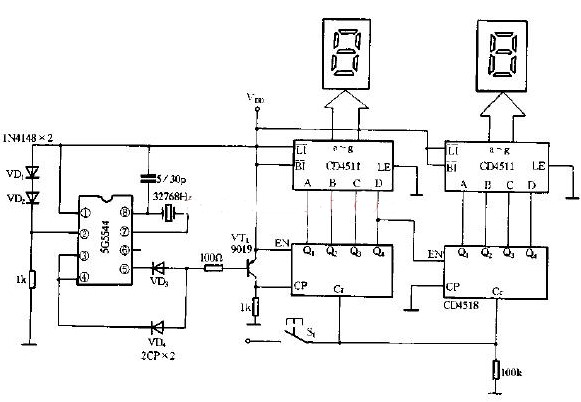

数字秒表由计数显示电路、复位电路、控制电路与电源电路组成。通过计数电路、译码电路在显示器上输出,以上部分组成计数显示电路;通过电源清零电路和反馈清零电路实现复位功能,构成复位电路;利用启动开关和停止

2019-07-04 14:01

现场可编程门阵列(简称 FPGA)是20 世纪 80 年代中期出现的高密度可编程逻辑器件,采用SRAM开关元件的 FPGA 是易失性的,每次重新加电,FPGA 都要重新装入配置数据。突出优点是可反复编程,系统上电时,给 FPGA 加载不同的配置数据,即可令其完成不同的硬件功能。这种配置的改变甚至可以在系统的运行中进行,实现系统功能的动态重构。

2018-02-01 17:25

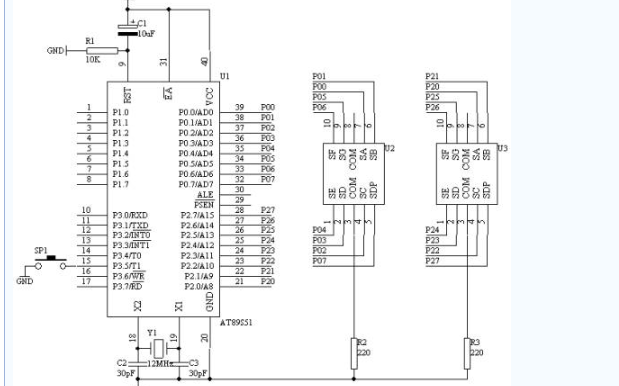

本电路由启动、清零复位电路、多谐振荡电路、分频计数电路、译码显示电路等组成。如下图所示:

2019-09-08 09:56

#define DIG_NONE 0xff; #define DIG_1 0x7f #define DIG_2 0xbf #define DIG_3 0xdf #define DIG_4 0xef #define DIG_5 0xf7 #define DIG_6 0xfb #define DIG_7 0xfd #define DIG_8 0xfe

2018-12-06 16:04

大学时代第一次接触FPGA至今已有10多年的时间,至今记得当初第一次在EDA实验平台上完成数字秒表、抢答器、

2018-03-20 14:07

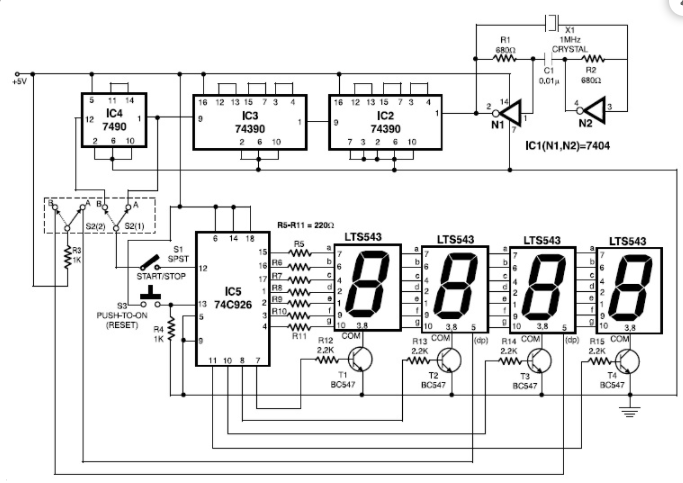

大学时代第一次接触FPGA至今已有10多年的时间,至今记得当初第一次在EDA实验平台上完成数字秒表、抢答器、密码锁等实验时那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

2018-12-15 09:54

简单的电路设计可用作精确的秒表,以 0.01 秒的测定计数最多 100 秒或以 0.1 秒的测定计数最多 1000 秒。该秒表可用于运动、游戏和其他类似的不同练习。

2022-06-27 16:34

1. 实验任务 (1. 开始时,显示“00”,第1次按下SP1后单片机秒表就开始计时。 (2. 第2次按SP1后,计时停止。 (3. 第3次按SP1后,计时归零。

2020-05-05 16:16

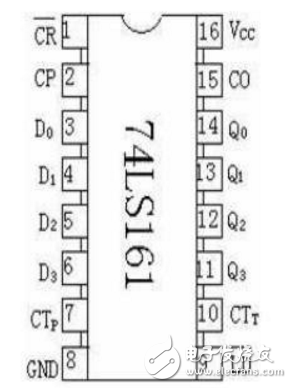

本文主要介绍了一种基于74LS161的简单秒表设计。74LS161是一种性能比较高,同时能量消耗较小的CMOS4位同步二进制加计数器,利用清零端口对数字进行清零,并且将低位计时器的输出,通过

2018-01-17 18:32