使用Verilog进行数字电路设计是一个复杂但有序的过程,它涉及从概念设计到实现、验证和优化的多个阶段。以下是一个基本的步骤指南,帮助你理解如何使用Verilog来设计数字电路: 1. 明确设计需求

2024-12-17 09:47

在当今电子技术行业发展过程中,对高速电路数字设计十分关注,高速数字电路是利用多个电子元件组成的,可以让计算机高速数字电路技术进一步提高,因此在计算机中使用高速数字电路设计

2020-08-21 17:41

本文介绍了EDA技术主要特点和功能,并对将EDA技术引入到数字电路设计工作方案进行了探讨。##EDA技术在数字系统中应用以基于AlteraEPM7128SLC84-15芯片和MAX PlusII 10.0软件平台数字

2014-01-24 14:38

对于高速数字电路而言,虽然还是关注电压,但是其设计方法和射频电路的设计方法相近,也需要考虑阻抗阻抗匹配,因为反射电压的存在会导致额外的误码率

2016-05-26 15:42

Quantus 是目前业界非常受信任的寄生参数抽取工具。在集成电路行业内,处于领先地位的制造厂商和设计公司都会大规模地应用该工具,尤其在工艺制程步入深亚微米的先进工艺领域(16 nm 及更先进的制程),Quantus 在模拟电路和

2022-09-27 14:40

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统

2017-02-11 13:04

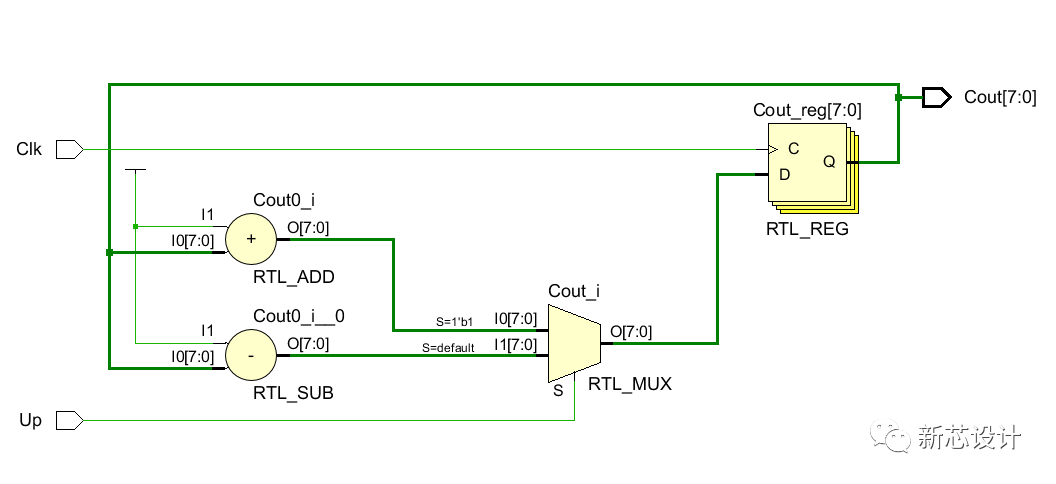

在数字系统中,使用得最多的时序电路差不多就是计数器了。计数器不仅能够用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲、产生脉冲序列以及进行数字运算等等。

2023-10-09 17:48

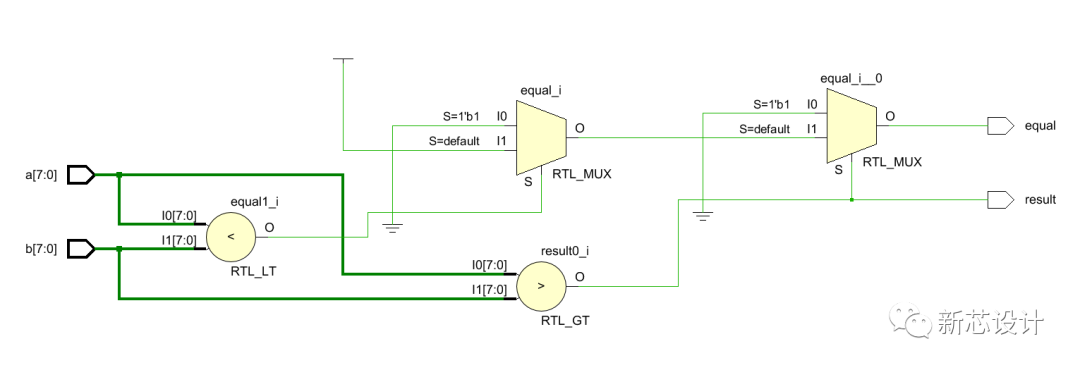

在数字系统中,总是需要对一些数据进行比较,比较两个数值甚至多个数值的大小,然后进行排序,于是,数值比较器(Comparator)的逻辑电路便应运而生。

2023-10-09 16:03

单片射频器件大大方便了一定范围内无线通信领域的应用,采用合适的微控制器和天线并结合此收发器件即可构成完整的无线通信链路。它们可以集成在一块很小的电路板上,应用于无线数字音频、数字视频数据传输系统,无线遥控和遥测系统,

2017-11-25 13:53

随着科学研究与技术开发市场化,采用传统电子设计手段在较短时间内完成复杂电子系统设计,已经越来越难完成了。EDA(EleCTRonICs Design Automation)技术是随着集成电路和计算机技术飞速发展应运而生一种高级、快速、有效电子设计自动化工具。

2016-05-10 15:45