电子设计自动化领域领先的供应商 Cadence,诚邀您参加 “ 2023 Cadence 中国技术巡回研讨会 - 数字设计与签核北京专场” 。会议将集聚Cadence 的开发者与资深技术专家,与您

2023-11-16 16:30

电子设计自动化领域领先的供应商 Cadence,诚邀您参加 “ 2023 Cadence 中国技术巡回研讨会 - 数字设计与签核北京专场” 。会议将集聚Cadence 的开发者与资深技术专家,与您

2023-12-07 09:30

效率,从而提高客户的生产效率 新思科技(Synopsys, Inc., 纳斯达克股票代码:SNPS)近日宣布,凭借其行业领先的黄金签核产品组合, 公司已与三星晶圆厂展开合作,以实现经过充分认证的流程,显著提升准确性、

2021-01-11 18:21

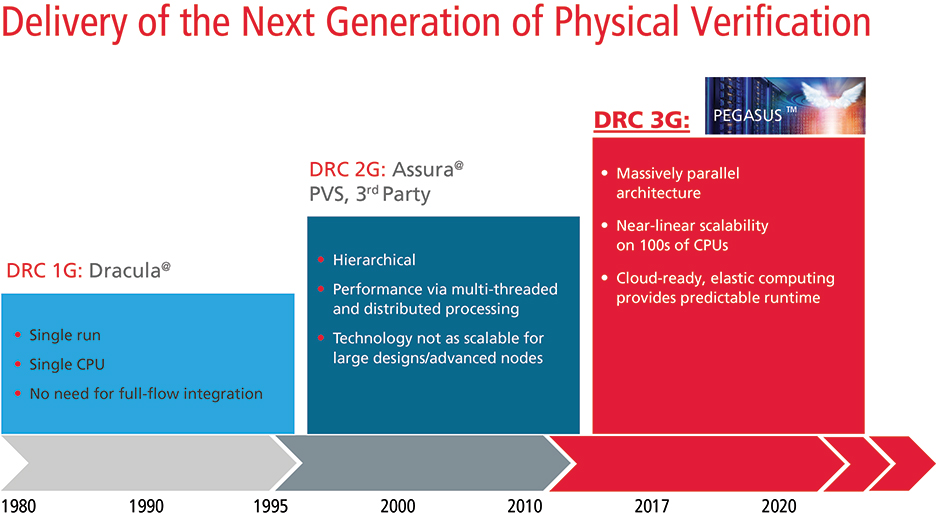

将助工程师缩短先进节点IC的上市时间。Pegasus™验证系统解决方案是全流程Cadence数字设计与签核套件的新成员,可扩展至数百CPU,设计规则检查(DRC)性能最

2017-04-14 15:42

电子设计自动化领域领先的供应商 Cadence,诚邀您参加“2023 Cadence 中国技术巡回研讨会”。会议将集聚 Cadence 的开发者与资深技术专家,与您分享数字设计与签核解决方案,并与

2023-10-23 11:55

电子设计自动化领域领先的供应商 Cadence,诚邀您参加“2023 Cadence 中国技术巡回研讨会”。会议将集聚 Cadence 的开发者与资深技术专家,与您分享数字设计与签核解决方案,并与

2023-10-30 11:35

上述流程会用到两个主要工具,分别是用于模块层次优化的 Tempus ECO,以及用于 SoC 层面静态时序分析的 Tempus STA。这里缺失了全芯片(或子系统)优化与签核。至于分区间功耗恢复等则只能忽略,因为实在

2022-11-01 14:18

新思科技3DIC Compiler集成了3Dblox 2.0标准,可用于异构集成和“从架构探索到签核”的完整解决方案。

2024-01-12 13:40

数字全流程提供了支持台积电 N4P 和 N3E 工艺技术的几个关键功能,包括从合成到签核工程变更单(ECO)的原生混合高度单元行优化,可实现更好的 PPA;基于标准单元行的放置;与

2022-10-27 11:01

新思科技近日宣布与Ansys联合开发的电压时序签核解决方案已获三星采用,用以加速开发其具有理想功耗、性能和面积(PPA)的高能效比设计。

2022-04-24 15:27