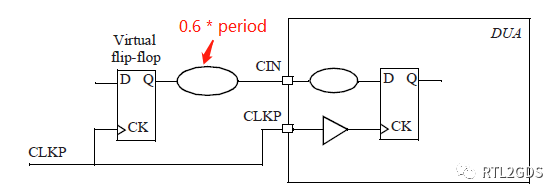

本文将对源同步定时如何优化高速接口时序裕量进行讨论。时序预算是对系统正常工作所需时序参数或时序要求的计算。

2012-03-20 10:46

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

2023-06-02 16:01

UART用一条传输线将数据一位位地顺序传送,以字符为传输单位 通信中两个字符间的时间间隔多少是不固定的, 然而在同一个字符中的两个相邻位间的时间间隔是固定的数据传送速率用波特率来表示, 指单位时间内载波参数变化的次数, 或每秒钟传送的二进制位数

2017-12-06 14:34

TMS320F2812慢速外设接口的时序控制 TMS320F2812通常能够实现与常用外围芯片的时序匹配,如RAM、D/A等;但是,当遇到读、写周期十分缓慢的输入/输出设

2009-09-27 16:33

IO约束在顶层和模块级的主要命令都是以下几个,但是实际应用的复杂程度不可同日而语,本篇会先介绍模块级IO约束实战经验,然后讲解顶层IO约束复杂性,过程中会介绍DDR接口时序。

2023-06-27 15:07

本应用笔记介绍了与DS80C320以外的Maxim高速微控制器的外部存储器接口。使用这些微控制器的系统设计人员必须了解不同器件系列的多路复用地址/数据锁存要求和锁存参数。讨论了EPROM和SRAM参数,以确保微控制器和外部器件之间的正确匹配。

2023-03-01 13:56

达拉斯半导体的DS80C320处理器由于吞吐量的提高,提供了广泛的新应用机会。然而,速度的提高还需要注意与处理器接口的内存的时序要求。本应用笔记确定了与存储器接口相关的关键时序

2023-01-10 10:18

本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列

2022-12-13 11:20

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建

2022-08-02 09:54

异步时序电路是指电路中除以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路中没有统一的时钟;电路状态的改变由外部输入的变化直接引起。

2019-11-29 07:07