电子发烧友

6886次浏览

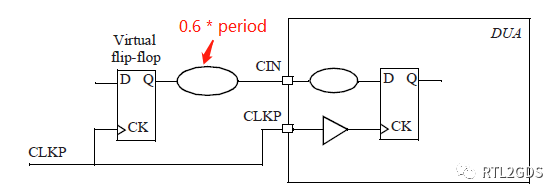

本文将对源同步定时如何优化高速接口时序裕量进行讨论。时序预算是对系统正常工作所需时序参数或时序要求的计算。

2012-03-20 10:46

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

2023-06-02 16:01

SCCB的总线时序与I2C基本相同,它的响应信号ACK被称为一个传输单元的第9位,分为Dont care和NA。Dont care位由从机产生;NA位由主机产生,由于SCCB不支持多字节的读写,NA位必须为高电平。另

2011-03-26 16:00

UART用一条传输线将数据一位位地顺序传送,以字符为传输单位 通信中两个字符间的时间间隔多少是不固定的, 然而在同一个字符中的两个相邻位间的时间间隔是固定的数据传送速率用波特率来表示, 指单位时间内载波参数变化的次数, 或每秒钟传送的二进制位数

2017-12-06 14:34

电子发烧友网站提供《嵌入式系统外围接口的时序分析与电路设计.pdf》资料免费下载

2023-10-09 16:50

这是TFT LCD RGB接口时序图,同步信号以及前肩后肩它们为什么都要”+1“?图中VSPW为场同步信号脉宽,HSPW为行同步信号脉宽,还有前肩后肩,可它们为什么都要+1?不理解啊,查编了资料都没有说明这一点的,没辙了,有懂这个的大牛吗?帮帮小弟吧,不胜感激,

2016-01-14 17:00

本文详细分析了ADSL系统中ATM层和物理层之间的UTOPIA LEVEL2接口时序,采用FPGA实现了UTOPIA接口设计,应用在ADSL系统中,数据收发正确,工作稳定;该方案的实现对解决现有专门通信芯

2010-07-28 16:54

TMS320F2812慢速外设接口的时序控制 TMS320F2812通常能够实现与常用外围芯片的时序匹配,如RAM、D/A等;但是,当遇到读、写周期十分缓慢的输入/输出设

2009-09-27 16:33

IO约束在顶层和模块级的主要命令都是以下几个,但是实际应用的复杂程度不可同日而语,本篇会先介绍模块级IO约束实战经验,然后讲解顶层IO约束复杂性,过程中会介绍DDR接口时序。

2023-06-27 15:07

频率30kHz"54kHz,垂直扫描频率50Hz"120Hz,带宽75MHz。基于DSPBuilder的VGA接口设计方法本设计需要完成的功能包括产生VGA时序以及基于VGA接口

2019-06-04 05:00