文介绍了FIR抽取滤波器的工作原理,重点阐述了用XC2V1000实现FIR抽取滤波器的方法,并给出了仿真波形和设计特点。

2018-04-19 11:34

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR

2018-04-28 11:50

设计了采样频率为640 MHz、过采样率为64的高频数字抽取滤波器。该数字抽取滤波器由CIC(Cascaded Integrator Comb)

2018-02-21 12:08

针对软件无线电接收机数字下变频中高速数字信号的降采样需求,利用半带滤波器及级联积分梳状滤波器,设计了一种半带滤波器前置的多级抽取

2017-11-17 09:01

数字抽取滤波器是ΣΔADC(ΣΔAnolog-to-Digital Converter)的重要组成部为分,旨在从高速、低分辨率的调制信号中重构出高分辨率、奈奎斯特频率的信号。为节约硬件资源,同时满足

2018-06-29 14:32

设计数字下变频器的抽取滤波器是一项艰巨任务。本文介绍一种能够完成此项任务的简便、易于理解的流程。

2018-07-13 08:13

前端的调制器利用过采样的方法将量化噪声搬移到高频段,后端的数字抽取滤波器必须再将高频噪声滤除,所以数字抽取滤波器的性能在

2018-07-18 18:31

我们将再次以AD9680为例。在这种情况下,无论速度等级如何,归一化抽取滤波器响应都是相同的。抽取滤波器响应仅随采样速率成比例。在此包含的示例

2023-06-30 15:43

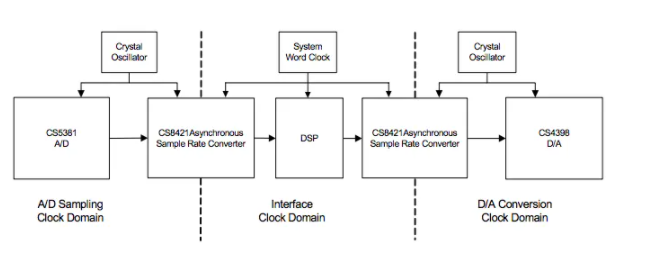

本应用笔记将介绍带有异步抽取滤波器的音频模数转换。它提出了转换过程对高频系统时钟的要求,并提出了这种音频转换的解决方案。 介绍 现代高性能 delta-sigma 模数 (A/D) 和数模 (D/A

2021-06-04 17:48

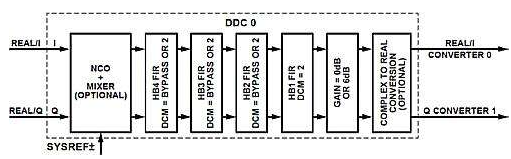

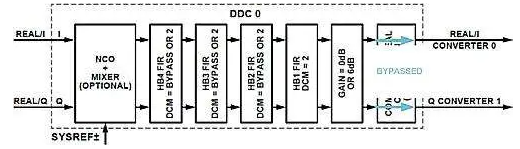

我们将继续以AD9680为例,就像在第1部分中所做的那样。与DDC的实际模式操作类似,无论速度等级如何,归一化抽取滤波器响应都是相同的。我想再次提到,对于此处包含的示例滤波器响应图,没有准确给出

2023-06-30 15:44