随着物联网移动终端的需求日益增长,对便携式设备与长续航能力的追求促使低电压和低功耗的芯片设计变得尤为重要。降低电路功耗而不牺牲其他性能指标是设计中的一大挑战。因此,想尽办法”压榨“电路中未能完全利用的电流,从而提高电流效率成为一种低功耗的设计思路。

2023-12-15 14:59

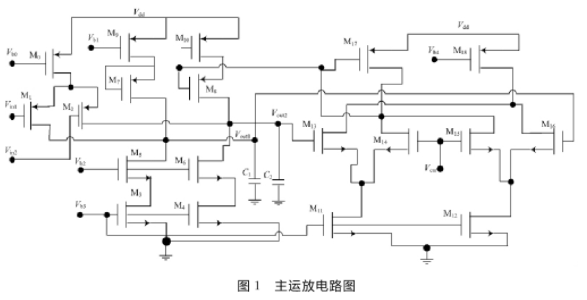

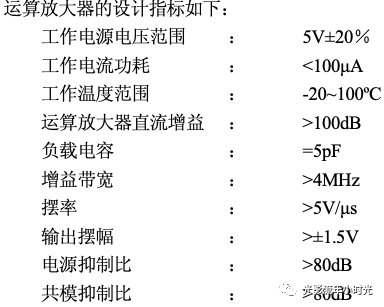

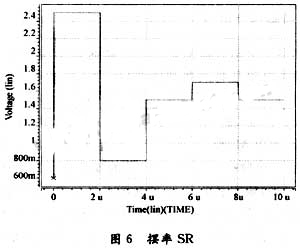

根据需要,本文设计运算放大器需要在较低的电压下能有大的转换速率、快的建立时间,同时要折衷考虑增益与频率特性及共模抑制比(CMRR)和电源抑制比(PSRR)等性能。

2020-12-18 12:10

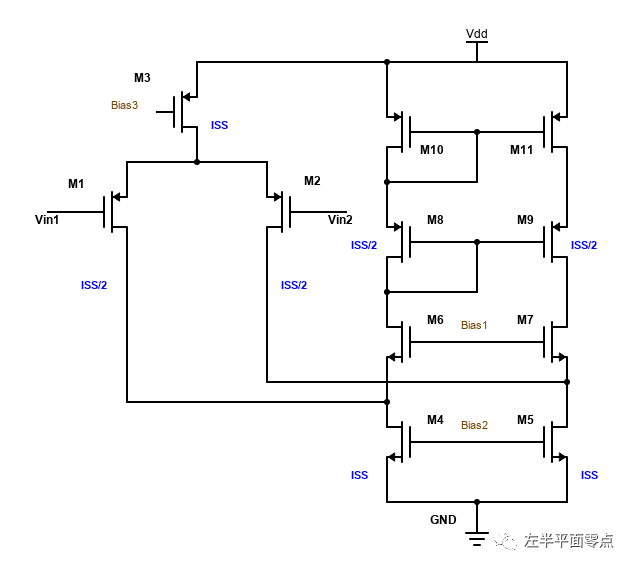

新型的复用型折叠式共源共栅运算放大器是从文献中折叠式

2012-03-08 10:12

本文设计了一种采用增益增强结构的带开关电容共模反馈的折叠式共源共栅跨导运

2011-06-29 09:45

由于设计的运算放大器的电压增益在 100dB 以上,因此通过前面各种电路结构的分析, 可以选择折叠式共源共栅电路和一个简

2023-09-25 17:37

本文设计的比较器是一个高增益的三级比较器,第一级为普通差分放大器,第二级为折叠式共源共栅差分放大器,第三级为

2011-08-10 10:23

折叠共源共栅放大器(Folded Cascode Amplifier)是一种在模拟集成电路设计中常用的放大器结构,它结合

2024-09-27 09:50

折叠共源共栅运算放大器原理及设计 1 引言 本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signa

2010-03-12 15:05

。放大器的输出较容易实现轨对轨, 但在输入端实现轨对轨是比较复杂的, 原则上只能是折叠式共源共栅结构才能使输入端包含电源

2018-12-18 09:15

的稳定性降低,另外,该结构下的折叠式共源共栅结构也会受体效应的影响,影响增益的恒定性。本文采用NMOS差分对结构,还对前

2020-07-24 10:11