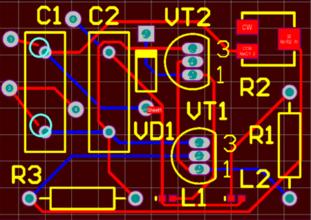

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。通过调整PCB布局布线,能够很好地防范ESD.尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100.对于顶层和底层表面都有元器件、具有很短连接线。

2016-01-20 09:59

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。

2015-04-07 15:30

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。

2023-11-20 15:28

在pcb板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。

2023-07-20 14:52

PCB设计时怎样抗静电放电 静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极

2010-03-13 14:55

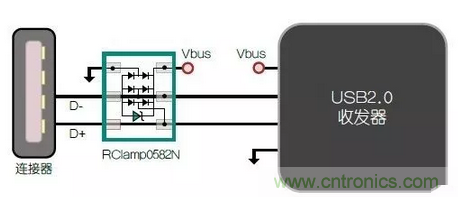

来源:罗姆半导体社区 微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的 IC。单次

2022-11-15 16:23

微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的IC。单次静电

2019-12-13 16:36

加重,甚至出现死灯现象,静电对LED品质有非常重要的影响。LED的抗静电指标绝不仅仅是简单地体现它的抗静电强度,LED的抗静电能力与其漏电值、整体可靠性有很大关系,更是

2021-07-15 15:40

本文介绍了手机静电放电测试的要求和方法, 总结分析了手机静电放电抗扰度试验的主要失效现象和模式, 可供手机

2011-10-20 10:02

静电放电的产生有两个基本条件,一. 是电荷的积累,电荷的积累是前提,然后是“跨接”,电荷的剧烈流动就是放电。所以从这两个方面就行控制就能有效地防护静电

2023-09-05 11:08