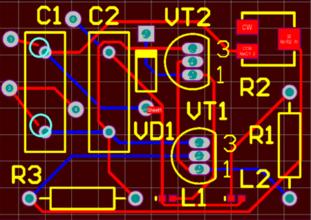

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。

2015-04-07 15:30

微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的IC。单次静电

2019-12-13 16:36

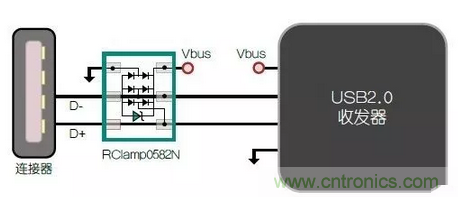

微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。这些祸害是隐秘的杀手,特别容易攻击敏感的IC。单次静电放电事件就可以将PCB送入地狱。

2018-06-05 15:40

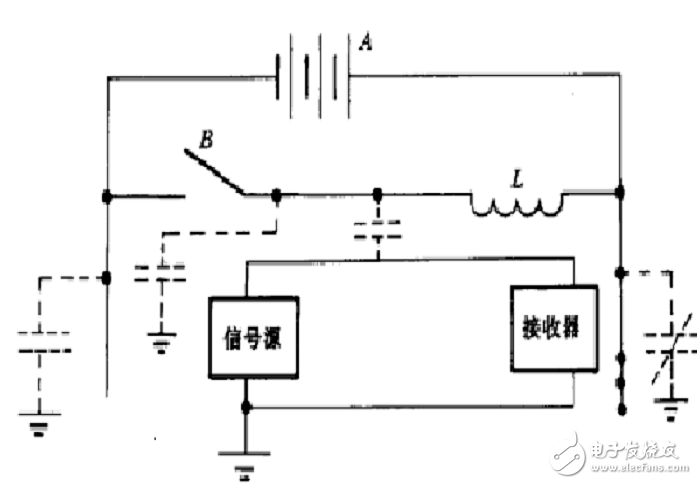

静电放电测试出现异常现象时,使用的辅助设备信息也很关键,不同的辅助设备可能出现不同的测试结果,测试时使用的线缆也应该关注。

2023-11-09 11:42

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。

2019-08-11 11:46

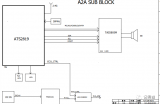

这期我带大家继续进行静电放电问题典型案例分析,前篇文章分别介绍了复位信号、DC-DC芯片设计问题引发的静电放电问题;这篇文章将介绍软件设计、PCB环路设计引发的

2023-12-11 10:03

依据标准IEC 61000-4-2/GBT17626.2的定义,静电放电就是具有不同静电电位的物体相互靠近或直接接触引起的电荷转移。 当人体穿着绝缘材料的织物并且对地绝缘时,在地面上运动时可能积累

2020-11-19 10:29

从这期开始我将带大家进入静电放电问题的典型案例分析,通过具体的实际案例以帮助大家消化前面的知识,并通过典型案例的分析为后面静电放电设计做铺垫。

2023-11-29 09:17

静电感应干扰是累积电荷高电压放电的电击现象。干扰表现是非持续性的,但是可以对电子设备造成永久性损害。用静电计可以测到。可以用抗静电措施与接地等

2018-01-18 14:18