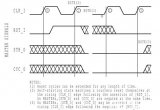

在图25的上升沿1,主设备发起操作,在上升沿2,从设备将ACK_O置高,在上升沿3,从设备知道主设备将发起新的操作,于是将ACK_O继续置高。因此, 3个时钟周期就完成了2次操作,而不是原来大的4个

2018-07-24 09:08

总线传输周期是计算机系统中数据传输的基本单位,它涉及到多个阶段,以确保数据能够正确、高效地在处理器、内存和其他外设之间传输。一个典型的总线传输周期通常包括以下四个阶段:

2024-10-12 09:05

如下图所示,除了时钟信号CLK和数据地址复用信号AD之外,PCI总线至少还应包括FRAME#(用于表示一次数据传输的起始)、C/BE#(Command/Byte Enable)、IRDY#

2018-04-08 08:52

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。时钟

2018-03-11 10:07

这些信号,以响应复位周期。RST_I被复位(变为0)后的第一个时钟上升沿到来后,主机接口的STB_O和CYC_O信号可以被立即置位(变为1)。

2018-07-11 09:07

在FPGA上实现一个模块,求32个输入中的最大值和次大值,32个输入由一个时钟周期给出。

2018-06-28 09:18

同步段是CAN总线位周期中每一位的起始部分。不管是发送节点发送一位还是接收节点接收一位都是从同步段开始的。但是由于发送节点和接收节点之间存在网络传输延迟以及物理接口延迟,发送节点发送一位之后,接收节点延迟一段时间才能接收到,因此,发送节点和接收节点对应同一位的同步

2020-03-26 10:13

时钟周期也称为震荡周期,定义为时钟脉冲的倒数,是计算机中最基本, 最小的时间单位。

2019-11-25 16:24

上次我们聊到了晶振的占空比,即信号在高电平持续时间与整个周期时间的比例。今天,我们来聊聊晶振频率信号中的脉冲、时钟周期和机械周期之间的关系。

2024-07-17 14:38

时钟周期也叫振荡周期或晶振周期,即晶振的单位时间发出的脉冲数,一般有外部的振晶产生,比如12MHZ=12×10的6次方,即每秒发出12000000个脉冲信号,那么发出一个脉冲的时间就是时钟

2022-12-19 10:57