本章介绍Verilog HDL的基本要素,包括标识符、注释、数值、编译程序指令、系统任务和系统函数。另外,本章还介绍了Verilog硬件描述语言中的两种数据类型。 3.1 标识符

2017-02-11 17:01

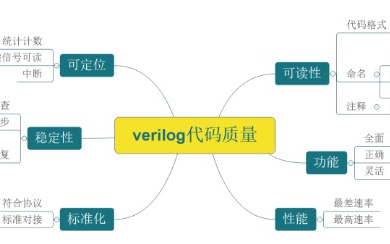

高质量的verilog代码至少需要包含以下几个要素:可读性、功能、性能、标准化、稳定性、可定位。

2023-07-18 10:09

Verilog HDL简称Verilog,它是使用最广泛的硬件描述语言。

2020-03-22 17:29

PCB LAYOUT術語解釋 PCB LAYOUT 術語解釋(TERMS)1. COMPONENT SIDE(零件面、正面)︰大多數零件放置之面。2. SOLDER SIDE(焊錫面、反面)。3. SOLDER M

2008-07-18 12:31

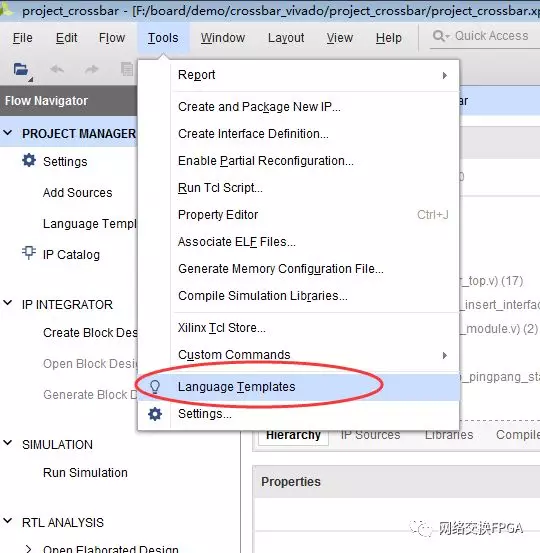

Verilog语言和VHDL语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把Verilog代码转换为VHDL代码。本文以通用的XHDL工具为例对Verilog转换

2020-11-10 15:41

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

高质量的verilog代码主要包含以下几个要素:可读性、功能、性能、标准化、稳定性、可定位。

2019-03-30 10:12

Verilog与C语言还是存在许多差别。另外,作为一种与普通计算机编程语言不同的硬件描述语言,它还具有一些独特的语言要素,例如向量形式的线网和寄存器、过程中的非阻塞赋值等。总的来说,具备C语言的设计人员将能够很快掌握Veri

2019-12-11 07:02

算法、算力和数据,是人工智能快速发展的三个要素。首先在算法上的突破,才让人工智能的商业化发展看到了希望。其次,计算能力的提升,使得复杂的算法得以实现,快速得出训练成果,降低成本。最后,大数据时代为人工智能的训练学习提

2020-12-18 09:40

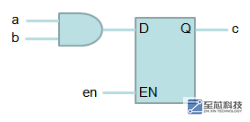

的電路。Introduction在C語言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。always@(a or b or en) if (en

2018-09-28 11:16