本章介绍Verilog HDL的基本要素,包括标识符、注释、数值、编译程序指令、系统任务和系统函数。另外,本章还介绍了Verilog硬件描述语言中的两种数据类型。 3.1 标识符

2017-02-11 17:01

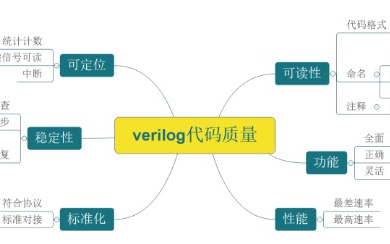

高质量的verilog代码至少需要包含以下几个要素:可读性、功能、性能、标准化、稳定性、可定位。

2023-07-18 10:09

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

高质量的verilog代码主要包含以下几个要素:可读性、功能、性能、标准化、稳定性、可定位。

2019-03-30 10:12

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及

2024-12-17 09:50

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

2024-12-17 09:44

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52

前面已经说到,模块名的定义要符合标识符的定义,那么什么是标识符呢?它的语法是什么呢?

2019-02-11 13:42

介绍几种自动生成verilog代码的方法。

2024-11-05 11:45

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设计的细节。 而且,一旦模块

2023-06-12 10:05