异步时钟切换电路

2014-05-08 09:40

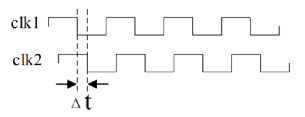

在异步系统中,由于数据和时钟的关系不是固定的,因此会出现违反建立和保持时间的现象。

2023-06-05 14:34

这种方法的效果与方法 3 相同。Vivado工具里面有‘-datapath_only’选项,这让设计者操作起来更简单,不用担心时钟偏移情况的发生。同时与 set_multicycle_path 方法相比,set_max_delay 方法更能表现出设计者的意图。

2019-07-29 18:05

当触发器输入端的数据和触发器的时钟不相关时,很容易导致电路时序约束不满足。本章主要解决模块间可导致时序 violation 的异步问题。

2023-03-28 13:46

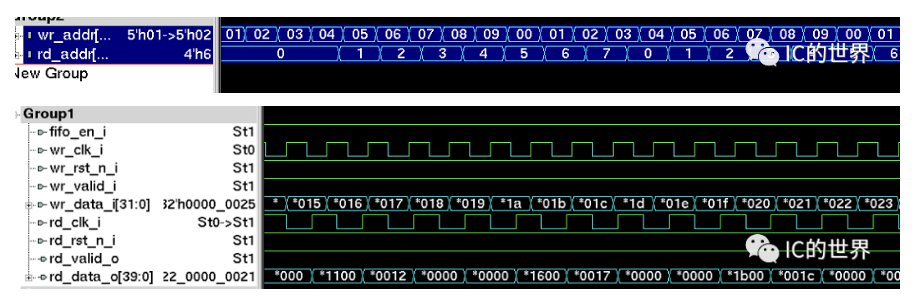

在进行模块设计时,我们经常需要进行数据位宽的转换,常见的两种转换场景有同步时钟域位宽转换和异步时钟域位宽转换。本文将介绍异步时钟

2023-11-23 16:41

现在的硬件设计中,大量的时钟之间彼此相互连接是很典型的现象。为了保证Vivado优化到关键路径,我们必须要理解时钟之间是如何相互作用,也就是同步和异步时钟之间是如何联系

2018-05-12 10:15

一、FIFO简介 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2022-11-15 09:29

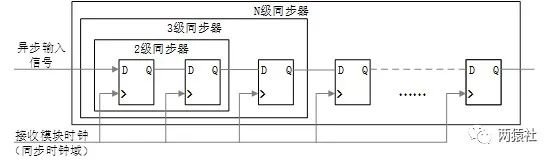

该方法只用于慢到快时钟域的1bit信号传递。在Xilinx器件中,可以使用(* ASYNC_REG = "TRUE" *)标记,将两个寄存器尽量靠近综合,降低 亚稳态因导线延迟太大而传播到第二个寄存器的可能性。

2025-05-14 15:33

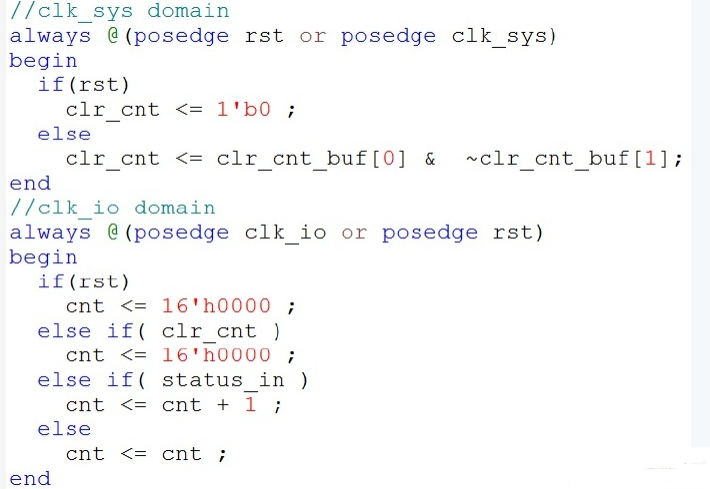

实际实现可能略有不同,CPLD逻辑在执行清零1)的同时会把”cnt”的值锁存下来,供CPU回读,也就是1)和3)也可以是一个步骤。这样表述是为了突出问题代码。

2020-10-21 14:25

最常用的约束有IO管脚位置约束和电平幅度约束,这个很好理解。另外,就是对时钟网络约束。这个是很重要的。比如你的系统中,驱动的电路的时钟是27M的,那么你需要在约束文件中增加类似如下的约束语句 NET

2021-09-13 09:29