异步时钟切换电路

2014-05-08 09:40

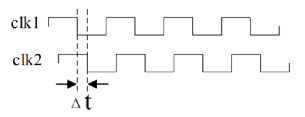

当触发器输入端的数据和触发器的时钟不相关时,很容易导致电路时序约束不满足。本章主要解决模块间可导致时序 violation 的异步问题。

2023-03-28 13:46

在进行模块设计时,我们经常需要进行数据位宽的转换,常见的两种转换场景有同步时钟域位宽转换和异步时钟域位宽转换。本文将介绍异步时钟

2023-11-23 16:41

该方法只用于慢到快时钟域的1bit信号传递。在Xilinx器件中,可以使用(* ASYNC_REG = "TRUE" *)标记,将两个寄存器尽量靠近综合,降低 亚稳态因导线延迟太大而传播到第二个寄存器的可能性。

2025-05-14 15:33

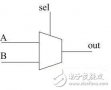

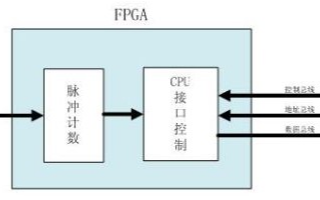

上次提出了一个处于异步时钟域的MCU与FPGA直接通信的实现方式,其实在这之前,特权同学想列举一个异步时钟域中出现的很典型的问题。也就是要用一个反例来说明没有足够重视

2020-03-03 10:10

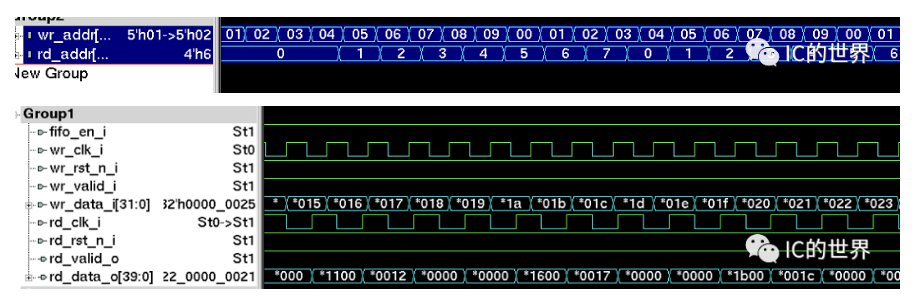

异步 FIFO 读写分别采用相互异步的不同时钟。在现代集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟,多时钟

2020-07-16 17:41

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。

2018-07-17 08:33

现代集成电路芯片中,随着设计规模的不断扩大。一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。

2014-05-28 10:56

IP核的全称是: AXI4-STREAM FIFO 设置注意事项:一定要选择异步时钟,也就是双时钟,如下: 关于其他配置: TLAST 一般要选择的,作为边界界定。其他可以不选。深度不必太深,因为只起到穿越

2018-03-26 14:40

CDC(不同时钟之间传数据)问题是ASIC/FPGA设计中最头疼的问题。CDC本身又分为同步时钟域和异步时钟域。这里要注意,同步

2022-05-12 15:29