本文主要介绍了时序设计和时序约束。

2023-07-04 14:43

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50

时序路径 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。 对于所有的时序路径,我们都要明确其起点和终点,这4类时序

2020-11-17 16:41

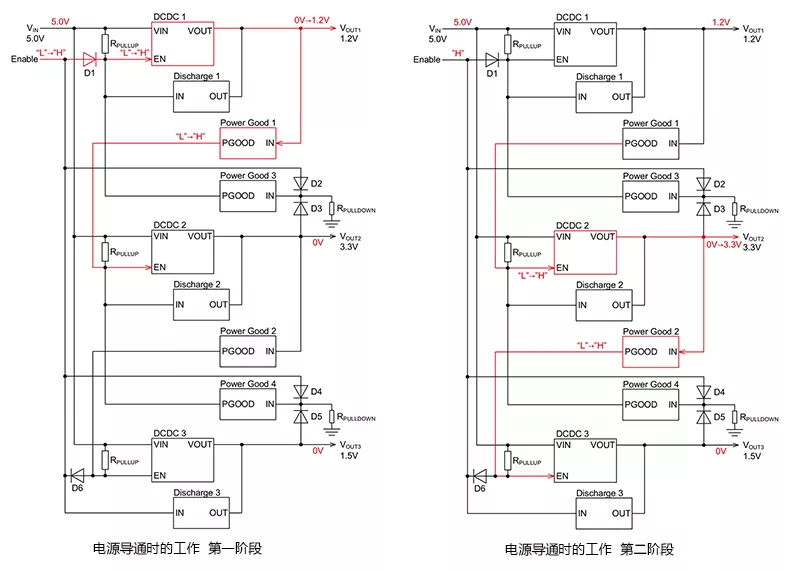

电源时序规格:电源导通时的时序工作

2023-12-08 18:21

由于FPGA技术和ARM技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA并行总线显得尤为重要。本文设计的FPGA的ARM外部并行总线

2013-08-15 10:44

本文继续讲解时序约束的第四大步骤——时序例外

2023-07-11 17:17

什么是数据并行传输,并行传输原理是什么? 数据通信的基本方式可分为并行通信与串行通信。 并行通信:是指利用多条数据传输线将一个

2010-03-17 16:25

并行除法器 ,并行除法器结构原理是什么? 1.可控加法/减法(CAS)单元 和阵列乘法器非常相似,阵列式除法器也是一种并行运算部件,采用大规模集成

2010-04-13 10:46

本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列

2022-12-13 11:20

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和

2022-04-21 08:55