由于FPGA技术和ARM技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA并行总线显得尤为重要。本文设计的FPGA的ARM外部并行总线

2013-08-15 10:44

本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列

2022-12-13 11:20

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和

2022-04-21 08:55

并行总线,就是并行接口与计算机设备之间传递数据的通道。采用并行传送方式在 微型计算机与外部设备之间进行数据传送的接口叫并行接口,它有2个主要特点;一是同时

2017-11-13 09:55

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Se

2020-08-31 13:49

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并

2017-11-18 04:32

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37

有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43

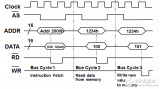

时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。如电子技术中的触发器、定时器、计数器等均用时序图来描述其工作原理。在plc顺序控制设计法编制梯形图程序时往往是先画出时序

2017-10-23 09:39