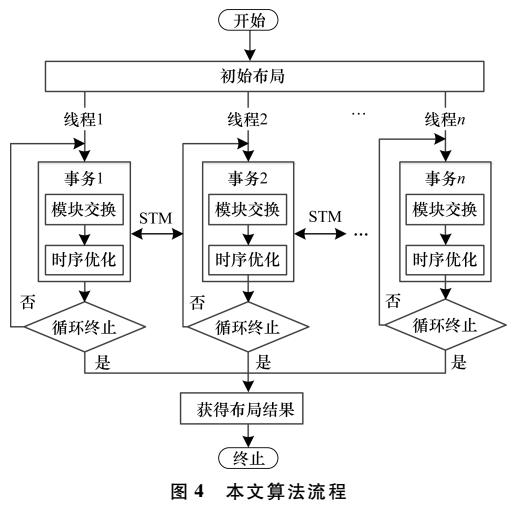

传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

2018-02-26 10:09

嗨,大家好,我总是使用我的设计之一,DCM提供3种不同的时钟频率。最近我决定在前一个版本中并行添加一个DCM,现在不再遵守时序约束。这是怎么可能的,因为新的DCM并行而不是关键路径?

2019-07-31 07:31

你好!请问当使用HMC625ALP5E的并行模式时时序是否是下面我理解的这样:当使用锁存并联时:首先将P/S脚置于低,是否是当LE置于低时,衰减状态由PUP1和PUP2决定,只有当LE输出一个高脉冲

2018-12-24 14:51

LCD显示模块的外部接口一般采用并行方式,并行接口接口线的读写时序常见以下两种模式: (1)8080模式。 这类模式通常有下列接口信号:Vcc(工作主电源)Vss(公共端)Vee(偏置负电

2022-02-09 07:34

时序约束与时序分析 ppt教程 本章概要:时序约束与时序分析基础常用时序概念QuartusII中的

2010-05-17 16:08

本文主要介绍了时序设计和时序约束。

2023-07-04 14:43

DSP型号:TI的 TMS320VC5509A(DSP5509)ADC型号:TI 的 DAC904(14位,时序图如图) 时序很简单,但问题是需要15个GPIO口,而该DSP的GPIO口才有7个

2015-03-30 19:00

DSP型号:TI的 TMS320VC5509A(DSP5509)ADC型号:TI 的 DAC904(14位,时序图如图) 时序很简单,但问题是需要15个GPIO口,而该DSP的GPIO口才有7个

2015-03-30 19:02

DSP型号:TI的 TMS320VC5509A(DSP5509)ADC型号:TI 的 DAC904(14位,时序图如图) 时序很简单,但问题是需要15个GPIO口,而该DSP的GPIO口才有7个

2015-03-30 19:03

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50