本文可让开发者们看懂 AMD Vivado Design Tool 2023.2 中的“AMD Versal Adaptive SoC CPM PCIE PIO EP 设计”CED 示例。

2024-05-10 09:39

基于Nios软核的SoPC系统设计是整个系统硬件设计的核心,包括Nios软核处理器的设计、数据采集控制的设计、图像信号FFT分析的实现、参数显示以及RS232通信模块的设计等。另外,使用Nios进行嵌入式设计在硬件上

2019-08-21 14:22

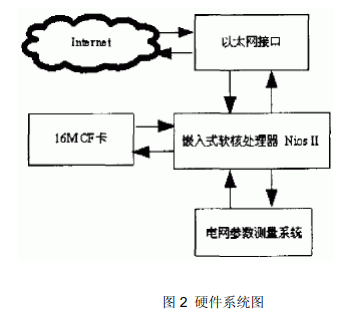

系统的硬件结构如图2所示。硬件系统的核心是构建于Ahera Cyclone FPGA中的Nios II嵌入式软核处理器。Nios II系列嵌入式处理器是一款通用的RISC结构的CPU,它定位于广泛

2020-06-28 14:49

东芝公司今日宣布推出无线充电接收器IC——“TC7766WBG”,该产品经认证符合无线充电联盟(WPC)制定的Qiv1.2 EPP(扩展功率分布)标准。TC7766WBG是业界[2]唯一一款通过Qi

2017-12-13 11:25

Z1有不锈钢、红古铜两种工艺,是中控智慧智能锁产品系列唯一一款不锈钢材质的智能锁,设计风格简单,产品定位是低价工程锁。

2019-12-03 09:59

Nios系统的所有外设都是通过Avalon总线与Nios CPU相接的,Avalon总线是一种协议较为简单的片内总线,Nios通过Avalon总线与外界进行数据交换。

2018-01-27 22:03

Views)自动的椎间盘定位以及量化的标注,充分利用Altera FPGA/Nios II资源,使系统小型化、便携化。该算法的应用,可以改善对骨质疏松引起的椎骨骨折进行自动的评估,对椎间盘进行量化分析,有助于与其他成像图像(如CT)进行图像的配准,以及图像引导的

2021-04-15 14:16

nRF24Z1能够以高达1.54Mbit/s的速率处理音频流,音频数据的输入/输出、射频协议和射频连接等工作由片内的硬件完成。图1所示为使用nRF24Z1的无线音频系统的结构框图,在该系统中,只需

2021-03-16 14:08

上一期我们从oneAPI CLI Samples Browser复制保存的Simple DMA是基于Quartus Pro的Nios V示例,无法直接用在DE1-SoC开发板上,因此这一节我们用

2025-06-23 11:17

大体上1Xnm工艺相当于16-19nm级别、1Ynm相当于14-16nm,1Znm工艺相当于12-14nm级别。

2020-03-22 14:28