HAC00304QN是一款2.1 GHz、4路输出的高性能差分时钟扇出缓冲器,输入时钟可从两个通用输入和一个晶体输入中选择。所选定的输入时钟被分配到三组输出,包含两组2

2025-07-13 15:27

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe

2023-06-08 15:30

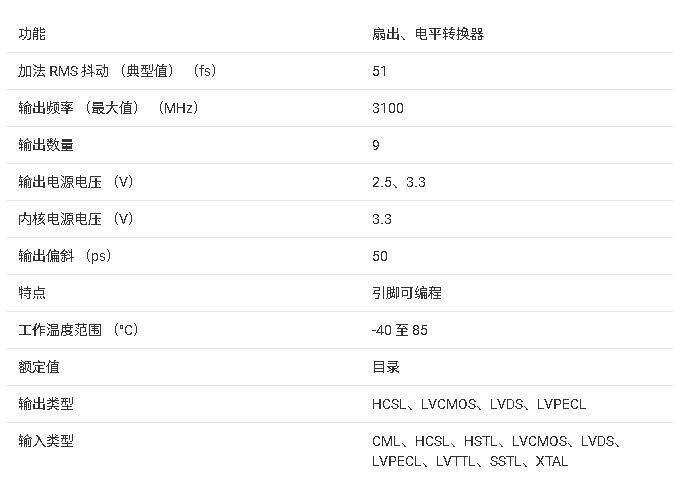

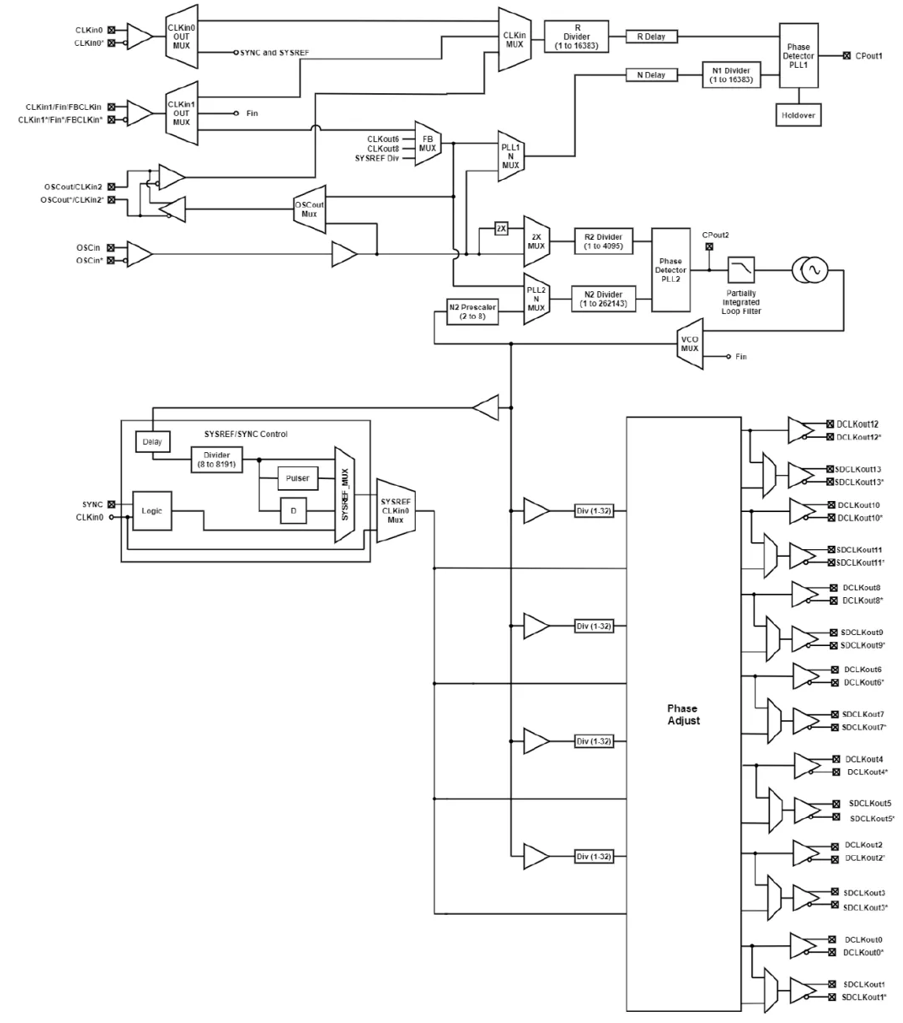

该LMK00306是一款 3 GHz、6 输出差分扇出缓冲器,适用于高频、 低抖动时钟/数据分配和电平转换。输入时钟可从两个 通用输入或一个晶体输入。选定的输入时钟分配给两个 3 个组

2025-09-15 14:45

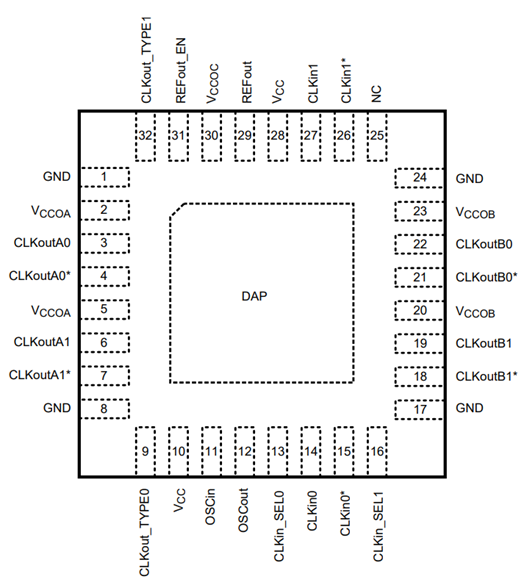

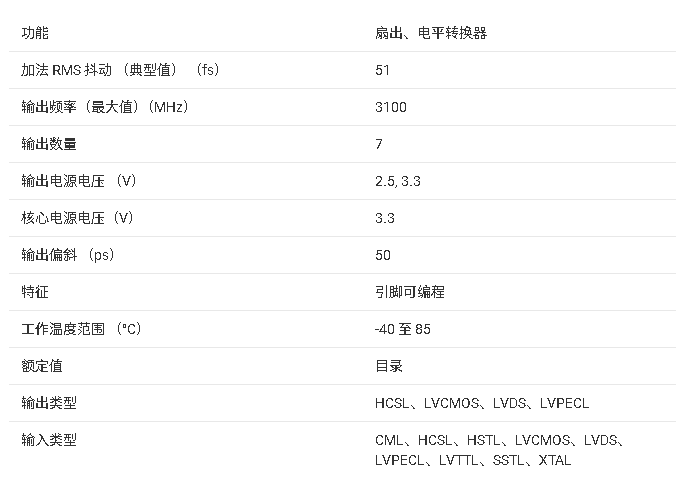

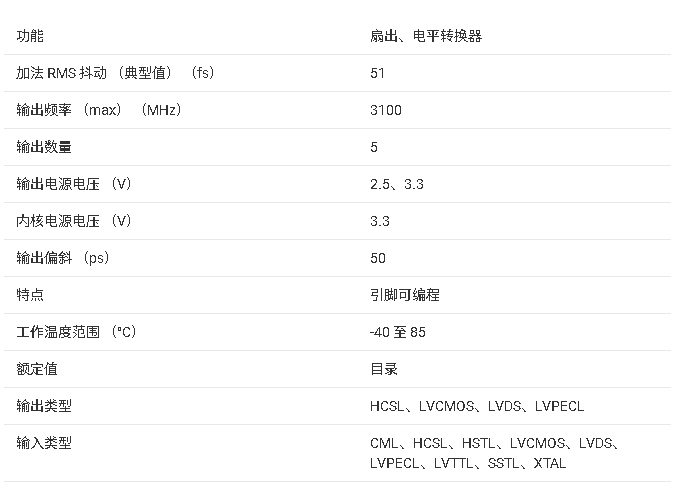

该LMK00304是一款3 GHz 4输出差分扇出缓冲器,用于高频、低抖动时钟/数据分配和电平转换。输入时钟可以从两个通用输入或一个晶体输入中选择。选定的输入时钟分配到两组2个

2025-09-15 14:50

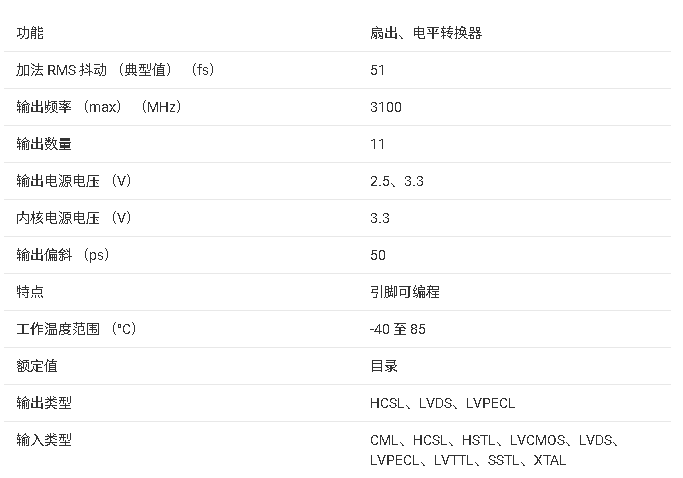

该LMK00301是一款 3 GHz、10 输出差分扇出缓冲器,用于高频、低抖动时钟和数据分配以及电平转换。输入时钟可以从两个通用输入或一个晶体输入中选择。选定的输入时钟分配给两组五个

2025-09-16 09:58

该LMK00308是一款 3 GHz、8 输出差分扇出缓冲器,用于高频、低抖动时钟/数据分配和电平转换。输入时钟可以从两个通用输入或一个晶体输入中选择。选定的输入时钟分配给两组 4 个

2025-09-15 14:55

目前国际国内局势复杂,本土科研机构及高端通信,导航,授时,信号处理与采集系统中通常会用到多路的高精度时钟,早期的工程师选型主要以TI的LMK系列型号以及ADI的HMC系列型号为主,国产芯片在此领域

2024-04-02 13:46

差分探头是一种常用的测量差分时钟时延的工具。差分时钟是指由两个相互关联的时钟信号组成的

2023-11-24 10:54

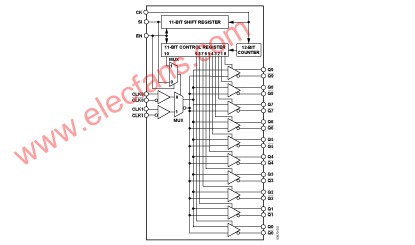

该ADN4670是一款低电压差分信号传输(LVDS)时钟驱动器,扩展的差分时钟输入信号到10差

2010-08-14 11:41