13、差分时钟EMC设计标准电路

2020-06-30 08:55

CLKIN为外部输入时钟,如果是外部差分时钟信号,在MHS文件的PORT行指定*_p、*_n管脚均为同样的Net,如dcm_clk_s,差分极性分别指定正负即可。

2017-02-11 05:12

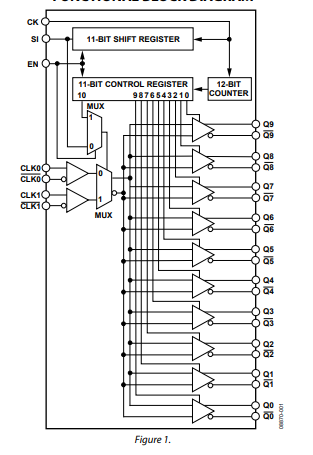

ADN4670是一款低压差分信号(LVDS)时钟驱动器,可以将一路差分时钟输入信号扩展为十路差

2025-04-10 16:19

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe

2023-06-08 15:29

LTC1346A 是一款单芯片收发器,其可采用 ±5V 电源为一个 V.35 接口提供差分时钟和数据信号。当与一个外部电阻器终端网络和一个用于控制信号的 LT 1134A RS232 收发器相结合时,LTC1346A 形成了一个完整的低功率 DTE 或 DCE V

2025-05-20 14:15

LTC1345 是一个采用单 5V 电源来为 V.35 接口提供差分时钟和数据信号的单片收发器。 与一个外部电阻终端网络和一个控制信号的 LT®1134A RS232 收发器配合,LTC1345 可形成一个采用单 5V 工作电源的完整低功耗 DTE 或 DCE V

2025-05-20 14:20

。解决了DDR SDRAM的差分时钟信号的反射问题和视频信号的串扰问题。本嵌入式系统经过实际调试后的时钟信号和视频信号满足设计要求,系统能够稳定工作。因此,在高速电路设计中,利用信号完整性理论进行仿真分析,对于指导工

2017-12-01 17:16

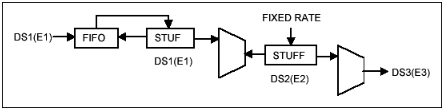

的特性,因此时钟将成对描述为DS3(E3)、DS2(E2)和DS1(E1)。本应用笔记阐明了发送时钟的频率容差、发送和接收时钟速率能力以及DS1/E1发送和接收

2023-06-13 15:39