结果表明,粘接层所受的应力主要集中在导电胶和芯片粘接界面边缘处,且粘接层四个角所受的应力最大,故在贴片工艺中要保证导电胶在芯片四个角的溢出,防止芯片脱落。适当增加导电胶的粘接层厚度,选取低弹性模量和低热膨胀系数的导电

2022-12-09 11:24

结果表明,粘接层所受的应力主要集中在导电胶和芯片粘接界面边缘处,且粘接层四个角所受的应力最大,故在贴片工艺中要保证导电胶在芯片四个角的溢出,防止芯片脱落。适当增加导电胶的粘接层厚度,选取低弹性模量和低热膨胀系数的导电

2022-12-12 15:51

在计算焊盘坐标时,数据手册中指定的芯片尺寸与从晶圆上切割后的物理芯片尺寸之间经常存在混淆。芯片的物理边缘不是引线键合的良好参考,因为整体芯片尺寸略有不一致。本应用笔记将

2023-06-16 17:23

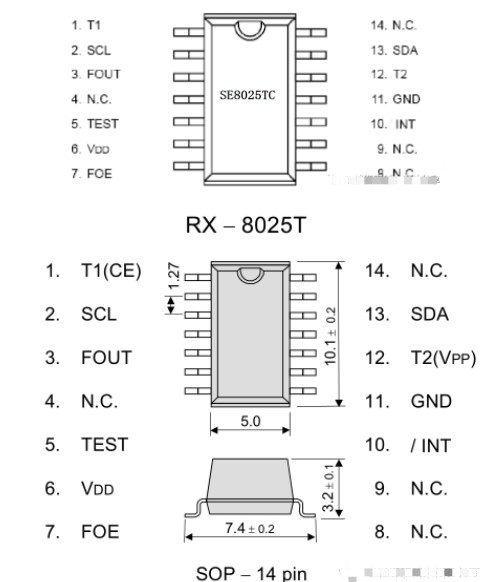

这颗芯片的空的pin太多了,这样就影响了芯片的体积,相对于小尺寸贴片封装来说,新设计的时候,还是要优先考虑使用小点封装的芯片,现在小

2022-08-30 16:31

Archer芯片实验室装置的生物传感器关键元件,已被微型化为纳米级尺寸的芯片格式,这是成功开发生物芯片所必须的。

2021-04-24 11:27

随着科技的飞速发展,高功率大尺寸芯片在数据中心、人工智能、高性能计算等领域的应用日益广泛。然而,这类芯片的高功耗和物理尺寸的扩展带来了严重的散热问题。据研究,

2025-03-21 13:11 北京中科同志科技股份有限公司 企业号

芯片制造商巨资进军移动领域 北京时间2月22日消息,据《纽约时报》报道,在美国,州立最先进的芯片厂投资一般要30亿美元。工厂要建几年,而且,微尺寸的芯片

2010-02-23 10:39

为了实现集成电路芯片的电通路,一般需要将芯片装配到在塑料或陶瓷载体上,这一过程可以称为CSP。CSP的尺寸只是略大于芯片,通常封装

2023-12-22 09:08

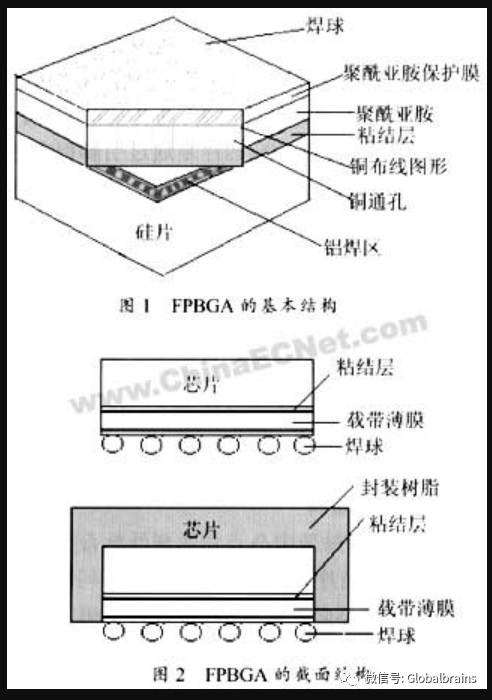

所谓芯片尺寸封装就是CSP (Chip Size Package或Chip Scale Package)。JEDEC(美国EIA协会联合电子器件工程委员会)的JSTK一012标准规定,LSI芯片封装

2023-09-06 11:14