在数字系统中,比较容易出现在低电平上叠加一个噪声正脉冲

2022-02-02 09:05

最近在看逻辑电路,刚刚看到编码器,发现二进制编码器是高电平输入有效,而优先编码器是低电平输入有效,于是就在想,同样都是编码器,为什么不去统一设置一个标准呢?上网搜了搜,

2020-05-18 10:47

它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象:我们有的同学可能已经学习了这样的一条PCB布线

2022-01-14 14:44

事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象: 我们有的同学可能已经学习了这样的一条PCB布线

2018-02-06 12:37

低电平有效的电路硬件设计要点必知

2021-06-28 15:28

能力更强。结合实际讲一个有用的例子来加深印象: 我们有的同学可能已经学习了这样的一条PCB布线规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平

2016-10-03 09:45

请教前辈,如何判定引脚的是低电平有效、还是高电平有效?

2013-10-02 22:19

请问High-Voltage Motor Control + PFC Kit v2.0的IPM的输入极性,PWM的输入是高电平有效还是低电平有效的?

2020-06-10 11:04

在数字电路中,"clk"通常指的是时钟信号(clock signal),它是一种周期性的信号,用于同步数字电路中的各种操作。时钟信号的高低电平有效性取决于具体的电路设计和应用场景。 1. 时钟信号

2024-07-23 11:24

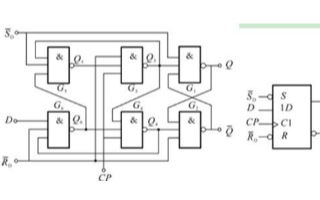

如何实现红方框内的输入低电平有效

2020-04-29 21:59