多年来,微波频率生成给工程师带来了重大挑战,需要深入了解模拟、数字和射频 (RF) 以及微波电子学,特别是锁相环 (PLL) 和压控振荡器 (VCO) 集成电路 (IC) 组件,同时还需要可调谐滤波、宽带放大和增益均

2022-12-20 15:54

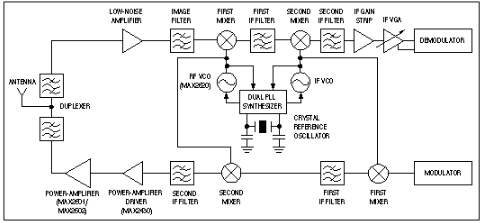

压控振荡器 (VCO) 的频率随施加到其调谐端口的电压而变化。VCO 在锁相环 (PLL) 中工作,为超外差接收器的频率转换提供稳定的本振 (LO)。VCO 还用于发射

2023-01-13 15:46

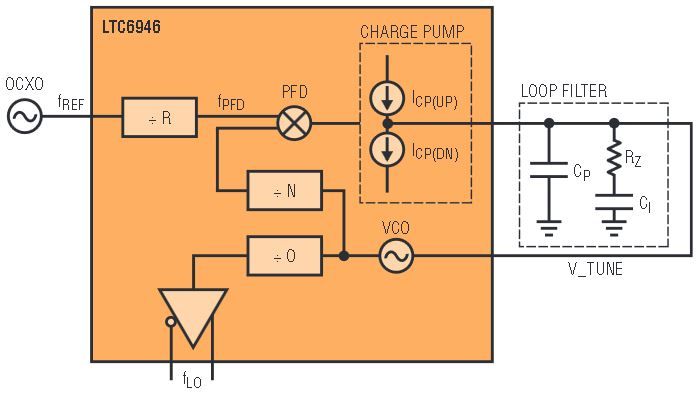

高带宽通信系统中的高数据吞吐量要求使得本振的相位纯度对于可靠性能至关重要。在此类系统中节省空间和成本的一种方法是使用结合PLL和VCO而不牺牲信号质量的IC。LTC6946 通过集成一个世界级的频率

2023-01-29 09:43

使用分立电路实现,可能需要高达30 V的电源电压。这给当今的PLL或RF系统设计人员带来了挑战:将低压PLLIC与更高电压的VCO接口。电平转换接口通常使用有源滤波器电路实现,下文将对此进行讨论。

2023-01-30 11:46

在PLL和VCO频率合成系统中,获得低于5 µs的频率和相位建立时间需极宽的环路带宽。环路带宽(LBW)定义控制环路的速度。更宽的LBW允许更快的建立时间,但会牺牲相位噪声和杂散信号的衰减能力。

2016-07-20 16:15

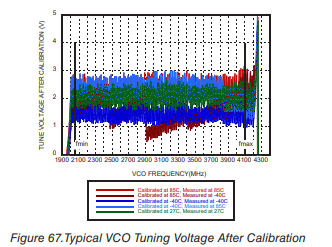

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和

2018-05-11 15:14

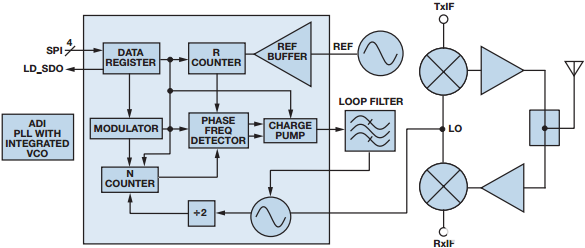

新型 PLL + VCO(带集成压控振荡器的锁相环)技术能够快速开发低相位噪声频率合成器解决方案,适用于 25 MHz 至 13.6 GHz 的蜂窝/4F、微波无线电和军事应用。

2023-01-09 15:30

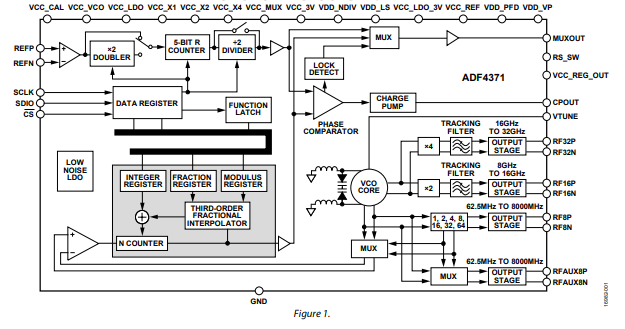

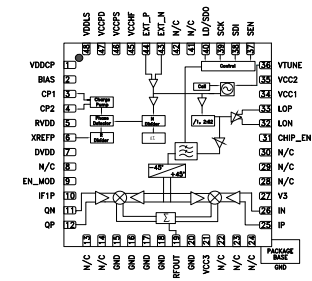

ADF4371 结合外部环路滤波器和外部参考频率使用时,可实现小数 N 分频或整数 N 分频锁相环(PLL)频率合成器。该微波宽带 VCO 设计允许产生 62.5 MHz 至 32 GHz 的频率

2025-04-25 10:10

HMC1190ALP6NE是一款集成PLL和VCO的高线性度宽带双通道下变频混频器,针对需要紧凑型、低功耗设计的多标准接收机应用进行优化。 HMC1190ALP6NE集成了宽带限幅LO放大器,可实现

2025-03-28 10:13

HMC1197是一款集成小数N分频PLL和VCO RFIC的低成本、高线性度直接正交调制器,非常适合0.1至4.0 GHz的数字调制应用,包括:蜂窝/3G、LTE/WiMAX/4G、宽带无线接入

2025-03-01 09:40