现代快闪存储器控制器中的磨损平衡技术已经有显著进步,能够克服快闪存储器储存介质固有的弱点,并帮助发挥出快闪存储器的优势。对于现代快闪

2018-03-07 09:45

基于当代DRAM结构的存储器控制器设计 1、引言 当代计算机系统越来越受存储性能的限制。处理器性能每年以60%的速率增长,

2009-12-31 10:57

用中档FPGA实现高速DDR3存储器控制器 引言 由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(D

2010-01-27 11:25

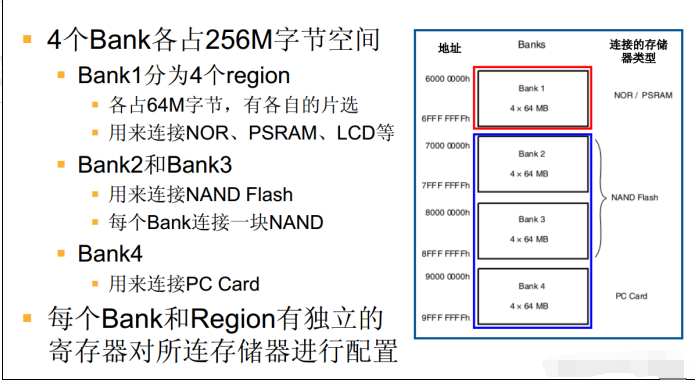

存储器共享控制器输出的地址、数据和控制信号,每个外部设备可以通过一个唯一的片选信号加以区分。 FSMC在任一时刻只访问一个外部设备。

2022-05-30 09:25

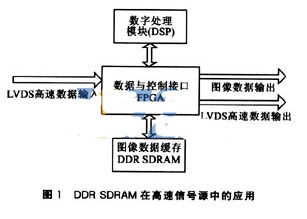

,因此能够很好地满足上述场合对大量数据缓存的需求。但DDR SDRAM的接口不能直接与现今的微处理器和DSP的存储器接口相连,需要在其间插入控制器实现微处理器或DSP对

2019-07-02 08:03

SMC 1000 8 x 25G支持下一代CPU和SoC所需的高存储器带宽,用于人工智能和机器学习。

2019-08-08 14:52

本视频介绍了可用于构建7系列FPGA内存控制器的软IP。 这些模块讨论了如何使用Xilinx存储器接口生成器构建存储器控制器以及MIG如何构建

2018-11-22 06:05

代快闪存储器控制器中的磨损平衡技术已经有显著进步,能够克服快闪存储器储存介质固有的弱点,并帮助发挥出快闪存储器的优势。对于现代快闪

2018-03-12 09:14

。 过去的DRAM不再用于较小的系统,因为它们需要DRAM控制器。SRAM进入了内存需求小的系统。DRAM进入更大的存储器,并伴随着用于更大存储器的控制器。 传统

2020-11-24 16:29

支持OMI的CPU或SoC可以使用具有不同成本、功耗和性能指标的大量介质类型,而无需为每种类型集成单独的存储器控制器。相比之下,目前的CPU和SoC存储器接口通常以特定的接口速率锁定在特定的DDR

2019-12-12 14:46