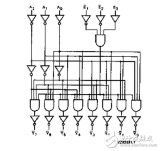

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

2017-10-31 17:15

用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54

2017-10-31 15:53

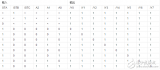

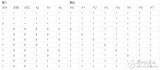

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1

2017-10-31 16:38

本文主要介绍了五款74ls138的应用电路图。其中包括了74ls138全加器电路、74ls138抢答器电路、74ls138

2018-05-04 10:31

什么是一位全加器,其原理是什么 加器是能够计算低位进位的二进制加法电路 一位全加器由2个半加

2010-03-08 17:13

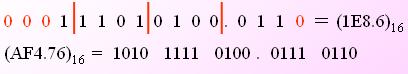

二进制数与十六进制数的相互转换 二进制数与十六

2009-09-24 11:28

74hc138的逻辑功能和74ls138是一样的。74hc138是高速CMOS芯

2017-10-31 11:19

二进制数的运算规则 二进制数之间可以执行算术运算和逻辑运算,其规则简单,容易实现。 (1) 加法运算规则 0

2009-10-13 16:24

74ls138引脚图

2007-12-17 22:33

4位二进制同步计数器74LS161引脚图及功能表 4位二进制同步计数器

2007-11-22 12:51