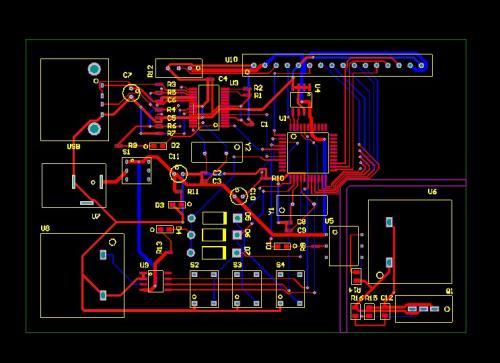

众所周知,在大部份设计软件中正常的流程是要先画原理图,生成网表,导入PCB设计软件,这种操作对于复杂的设计而言,是必要的流程,但是对于简单的设计而言,简直就是多此一举。我们知道在PADS中可能通过ECO模式,直接添加元件,建立网络。

2022-11-21 10:52

再做一个数字芯片封装的原理图时,希望隐藏电源引脚,但又希望把隐藏的引脚连接到指定的电源网络。 在AD17以及更早的版本中,如图有一个示例:我们隐藏第七个引脚,但是希望

2023-10-16 11:12

跳转/标号执行是用来跳过部分程序使其不执行必须用在同一程序块内部实现跳转。跳转/标号指令有两条,分别为跳转指令(JMP)和标号指令(LBL)。

2022-10-08 09:59

Altium Designer提供了6类网络标识:Net Label(网络标号),Port(端口),Sheet Entry(图纸入口),Power Port(电源端口),Hidden Pin(隐匿引脚)、Off-sheet Connector(图纸外连接符)。

2019-07-13 09:48

定位孔用于固定元件的位置,当元件受到外力作用时,定位孔周围的PCB板可能会发生变形或弯曲,进而导致附近走线断裂或元件焊接点开裂。因此,为确保电路板的可靠性,定位孔周围需要设置单边外扩0.5mm的禁布区。那么,在

2025-04-07 17:09

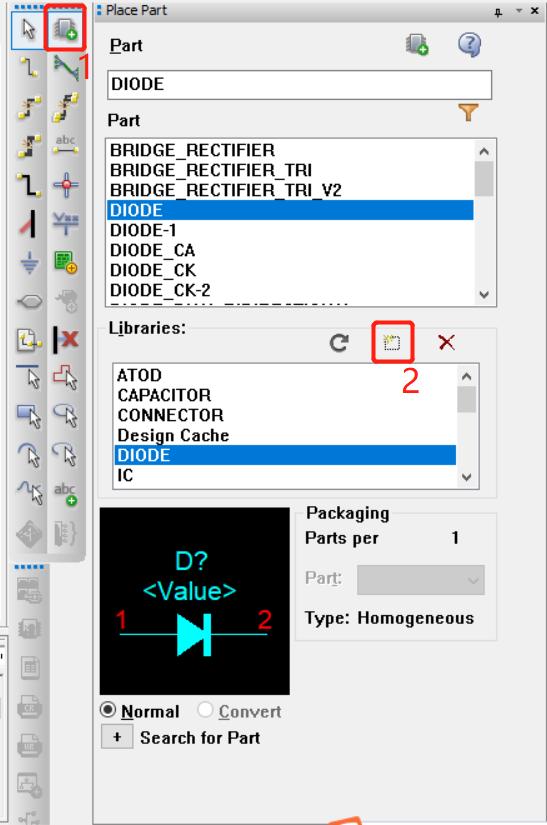

在使用cadence进行电子电路原理图设计时,突然发现一个问题,那就是cadence添加和导出原理图封装库的方式与altium designer还完全不一致。

2023-03-26 17:44

在绘画原理图的时候,就应该考虑需要在版图阶段作出的元件封装和焊盘图案决定。下面给出了在根据元件封装选择元件时需要考虑的一

2018-04-30 17:22

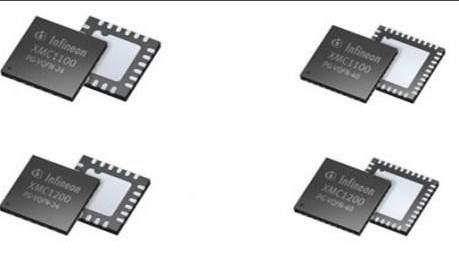

QFN是一种无引脚封装,呈正方形或矩形,封装底部中央位置有一个大面积裸露焊盘用来导热,围绕大焊盘的封装外围四周有实现电气连结的导电焊盘。由于QFN

2019-08-12 09:56

在PCB设计阶段,关于元件封装选择时需要考虑的以下六件事。本文中的所有例子都是用Multisim设计环境开发的,不过即使使用不同的EDA工具,同样的概念仍然适用。

2019-09-20 10:52

用三位或三位以上的数字组成,需要标明回路的相别或某些主要特征时,可在数字标号的前面(或后面)增注文字符号。

2019-06-05 14:47