丢失。 为了实现FPGA和DSP的同步时钟频率,可以采用以下两种方式: 1. 外部时钟源同步 通过引入外部时钟源,让

2023-10-18 15:28

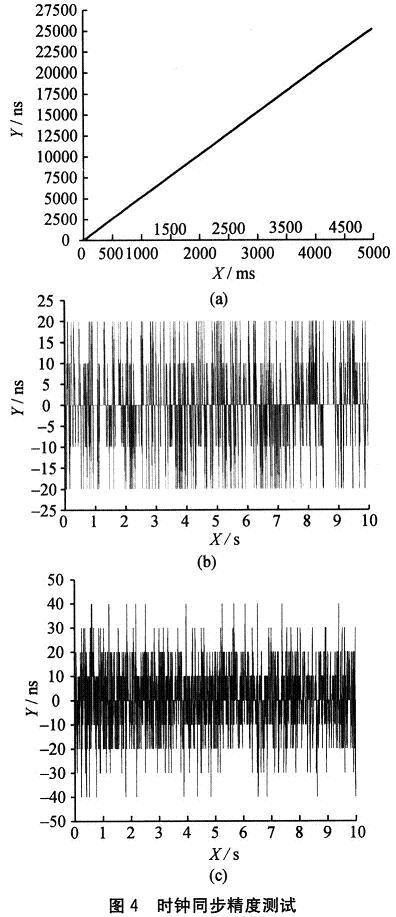

FPGA的时钟频率同步设计 网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速

2010-01-04 09:54

ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、

2022-11-23 16:50

“全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作

2023-07-24 11:07

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需

2012-05-21 11:26

如何改变spi的时钟频率? 改变SPI的时钟频率需要以下步骤: 1. 选择合适的时钟源和分频器:SPI接口的

2023-06-03 16:36

晶振是数字电路设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设

2021-04-07 12:00

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种

2009-12-27 13:28

使用示波器查看信号的频率是电子工程和物理学研究中的一项基本技能。示波器不仅可以显示信号的波形,还可以通过内置的测量工具来定量分析信号的特征,包括频率、周期、幅度等。

2024-05-17 15:37

时钟频率(又译:时钟频率速度,英语:clock rate),是指同步电路中时钟的基础

2017-11-10 14:21