差分线pcb走线原则 差分线是PCB设计中非常重要的一个部分,它的设计和走

2023-12-07 18:09

Altium Designer走差分线出现网格是什么原因? 答: 如图1所示,在AD软件中走

2022-12-10 07:45

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

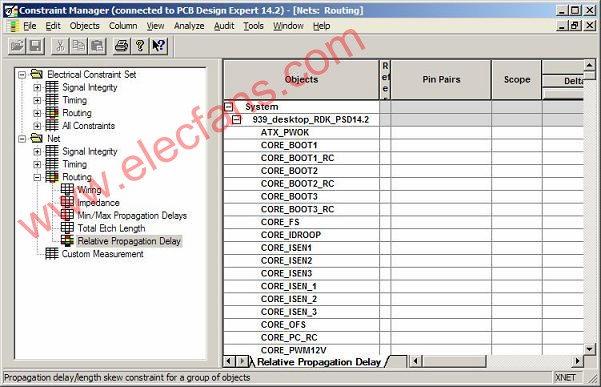

对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DD

2010-06-28 09:38

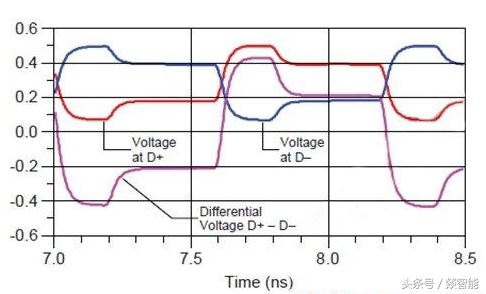

差分线用通俗的话讲,用两条平行的、等长的走线传输相位差180度的同一信号。说白了,就是一根线传输正信号,一根线传输负信号。正信号减去负信号,得到2倍强度的有用信号。而两

2022-02-12 10:10

有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着

2018-10-19 15:33

分线,千兆模式下是4对差分线。在部分PHY芯片的Datasheet或者应用手册中会给出MII/RMM/GMII/RGMII接口,MDI接口的等长规则,但是很少有厂家提到

2019-05-26 09:38

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29

PCB设计中常见的走线等长要求

2023-11-24 14:25

整个基础知识体系中,差分线(对)是很难搞的部分,却是最常用的部分。说到差分线基础知识,里面的概念很多,记得刚接触的时候,

2023-03-22 09:18