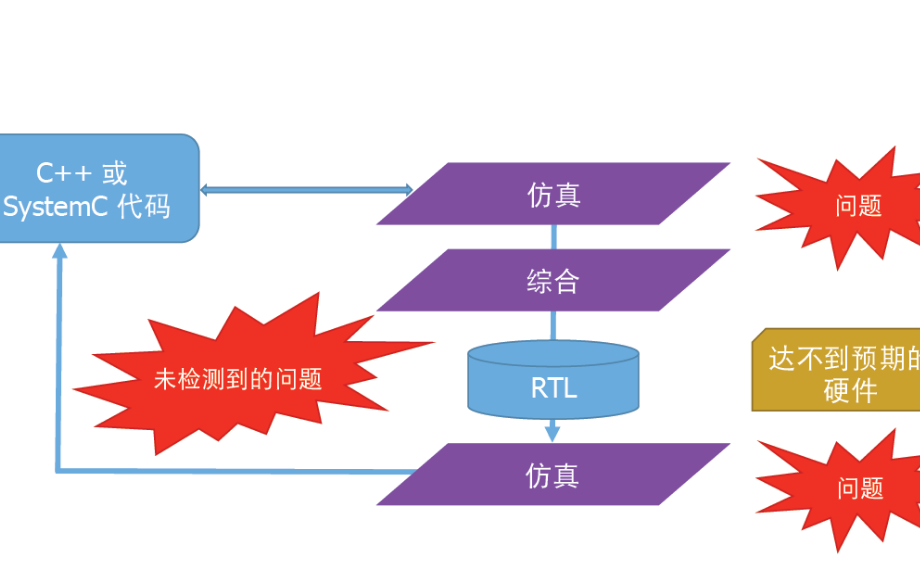

为了显著加快验证速度,处理每天都会变化的复杂算法,很多公司转向采用 High-Level Synthesis (HLS) 方法。但是,要利用在更高抽象度开展设计带来的相关性能改进,采用 C++ 或

2019-05-21 17:11

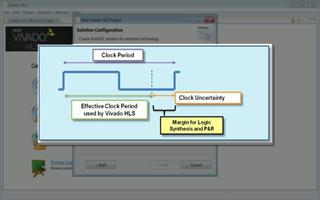

Xilinx公司讲述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47

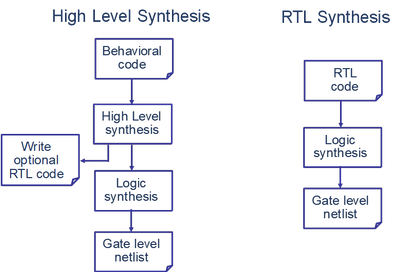

说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

2022-02-08 17:26

在上一章HLS的端口综合里有提及,HLS综合后的端口分为2中类型:BlockLevel和Port Level Interface。其中Port level是我们需要重点关注的,它又可以细分为4中类型

2017-02-08 03:27

在上一章,介绍了Block Level Interface。 本章里着重介绍下Port Level Interface的2中子类别:No I/O Protocol和Wire handshakes

2017-02-08 03:45

什么是CHILL (CCITT High Level Language) 英文缩写: CHILL (CCITT High Level Language)

2010-02-22 10:47

在前几章里,已经分别介绍了BlockLevel Interface,Port Level Interface中的NoI/O Protocol和AXI4。本章里着重介绍下Port Level

2017-02-08 02:42

Synthesis and Optimization4 Architectural-Level Synthesis and Optimization5 Scheduling Algorithms6 Resource

2009-07-23 08:55

想用Vivado做设计,然而介绍资料没有能够下载到。请朋友从外地下载,现在分享一下,希望对大家有帮助。

2020-01-02 20:00

在之前的3章里,着重讲解了HLS对AXI端口(包括axi-lite,axi-stream和full axi端口)的综合实现问题,下面让我们来介绍一下其它的端口类型是如何实现的。 在开始之前,先来

2017-02-08 03:39